PCB-Systemarchitektur-Konzeption

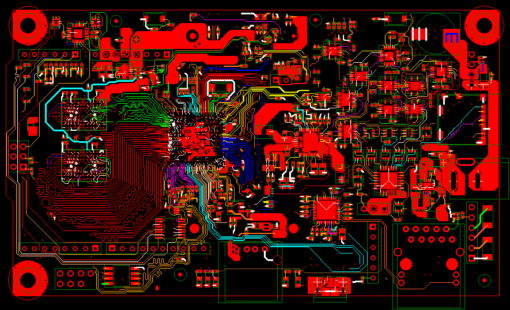

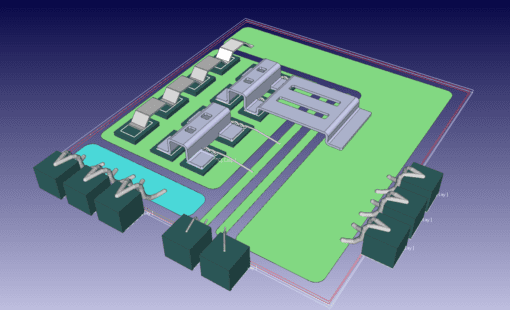

CR-8000 von Zuken ist die modernste PCB-Designplattform auf dem Markt. Sie bietet Architekturdesign und -verifizierung, Multi-Board-PCB-Layout mit MCAD-Integration, SI/PI-Analyse und Co-Design von Chip/Gehäuse/Board. CR-8000 eignet sich für Ihre anspruchsvollsten PCB-Systemdesigns.

Die Fähigkeiten von CR-8000 auf einen Blick

PCB-Systemarchitektur-Konzeption

Partitionierung komplexer Systeme in mehrere miteinander verbundene PCBs

Optimierung von IC, Package und PCB in einer durchgängigen Umgebung

Integriertes Datenmanagement für Versions-, Revisions-, und Konfigurationsverwaltung

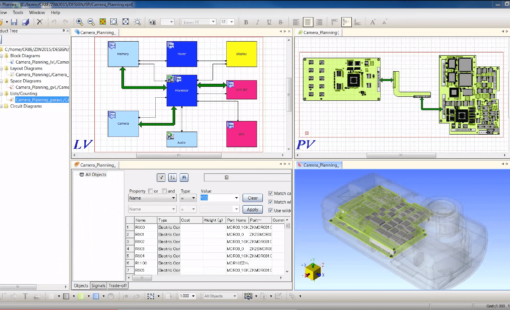

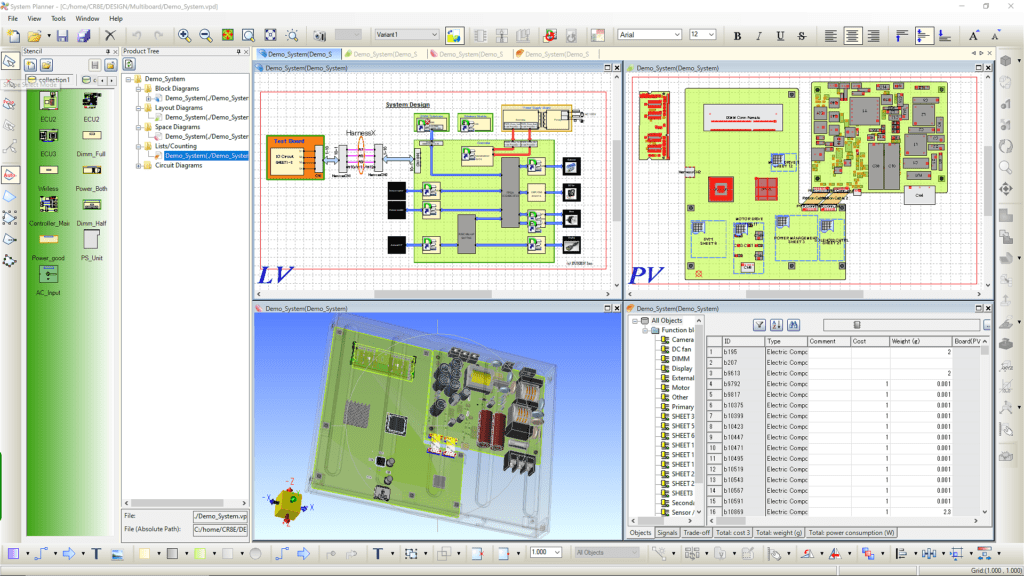

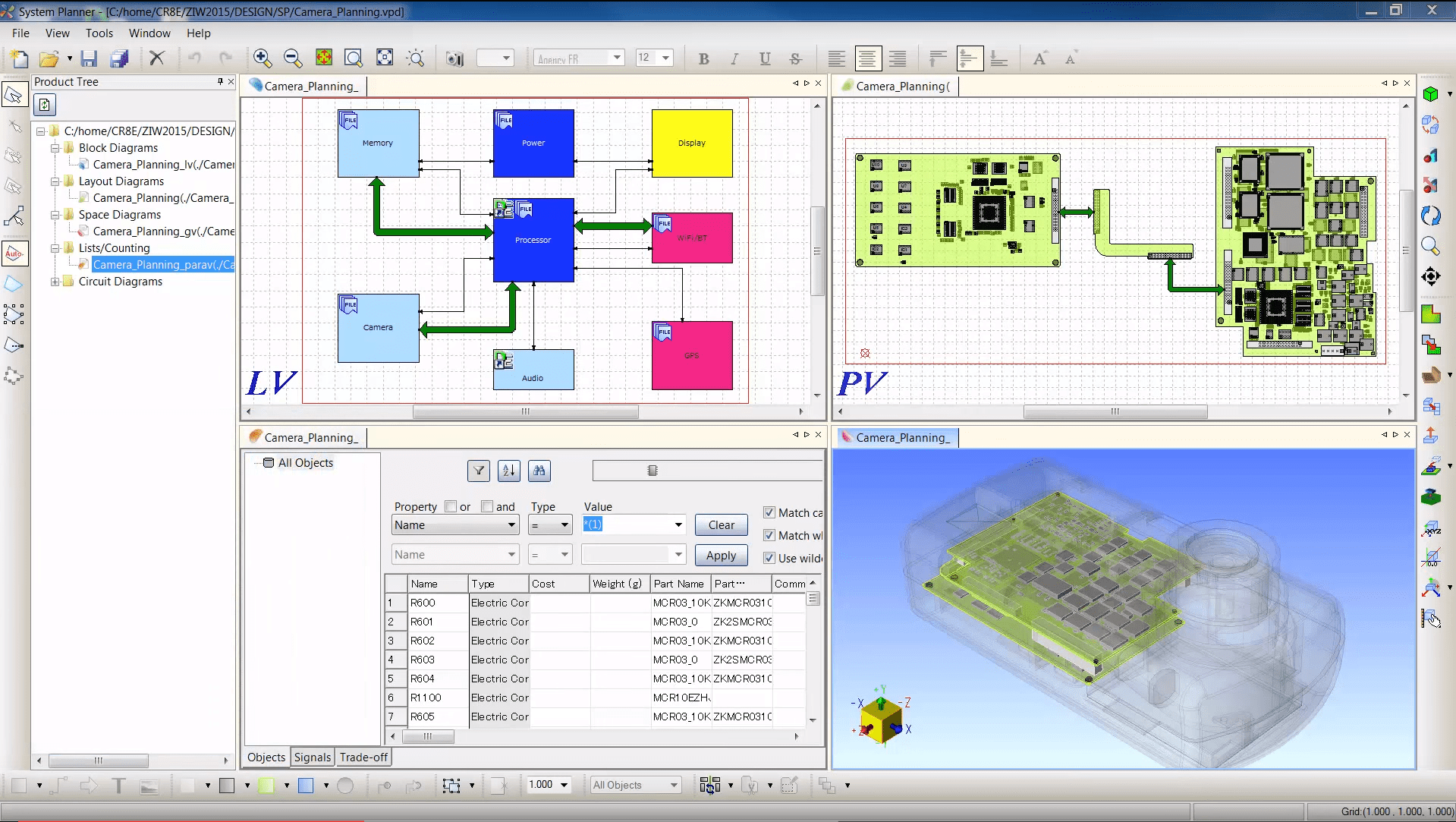

CR-8000 System Planner ist das einzige Design- und Verifizierungstool für PCB-Systemarchitekturen auf dem Markt, das vollständig in eine Entwicklungsumgebung für Leiterplatten und Kabelbäume integriert ist. Angesichts der zunehmenden Komplexität der Produkte ist die Optimierung der Architektur wichtiger denn je.

System Planner vereint vier Disziplinen in einem einzigen Design- und Analysewerkzeug.

Mit der Fähigkeit, Schaltungen auf Systemebene zu konzipieren, ermöglicht CR-8000 die Betrachtung und Optimierung eines elektronischen Systems in seiner Gesamtheit. Mit integrierten Simulations- und Analysewerkzeugen können sie das Verhalten des Systems, die Signalintegrität, die Stromverteilung und die thermischen Eigenschaften bewerten. So können potenzielle Probleme frühzeitig erkannt und korrigiert werden. Darüber hinaus bietet CR-8000 leistungsstarke Design-Regelprüfungen, mit denen sichergestellt wird, dass das Design den spezifischen Anforderungen und Standards unterschiedlicher Fertigungsstandorte entspricht. Diese Regeln sind konfigurierbar und decken verschiedene Aspekte wie elektrische, mechanische und fertigungstechnische Anforderungen ab.

Design Gateway

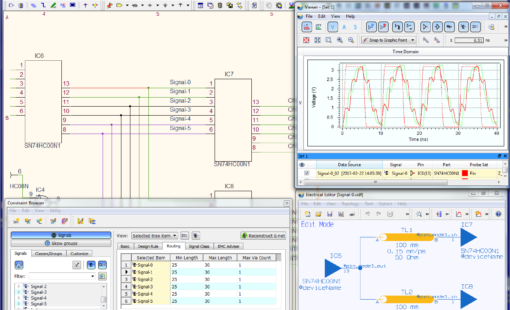

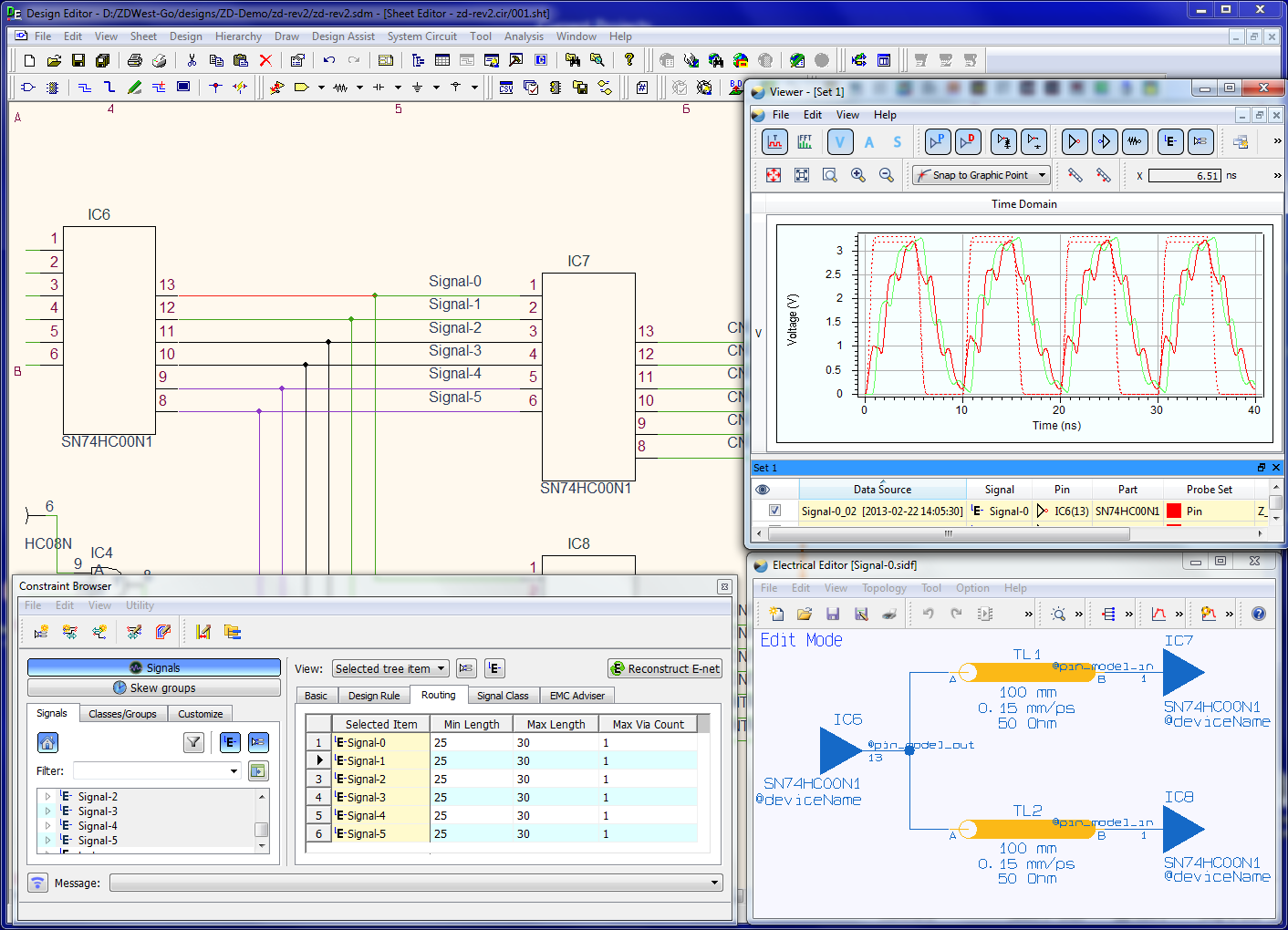

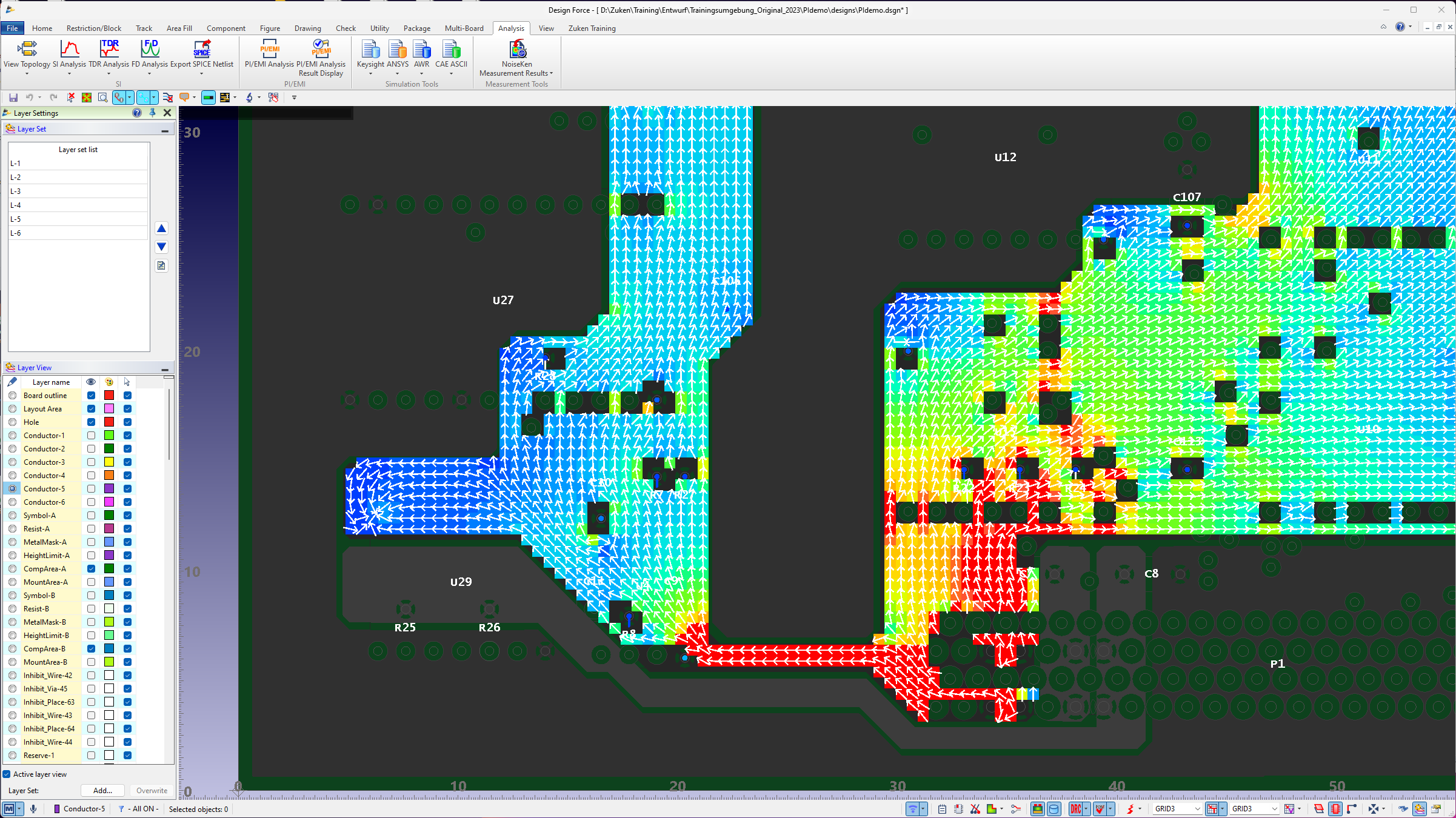

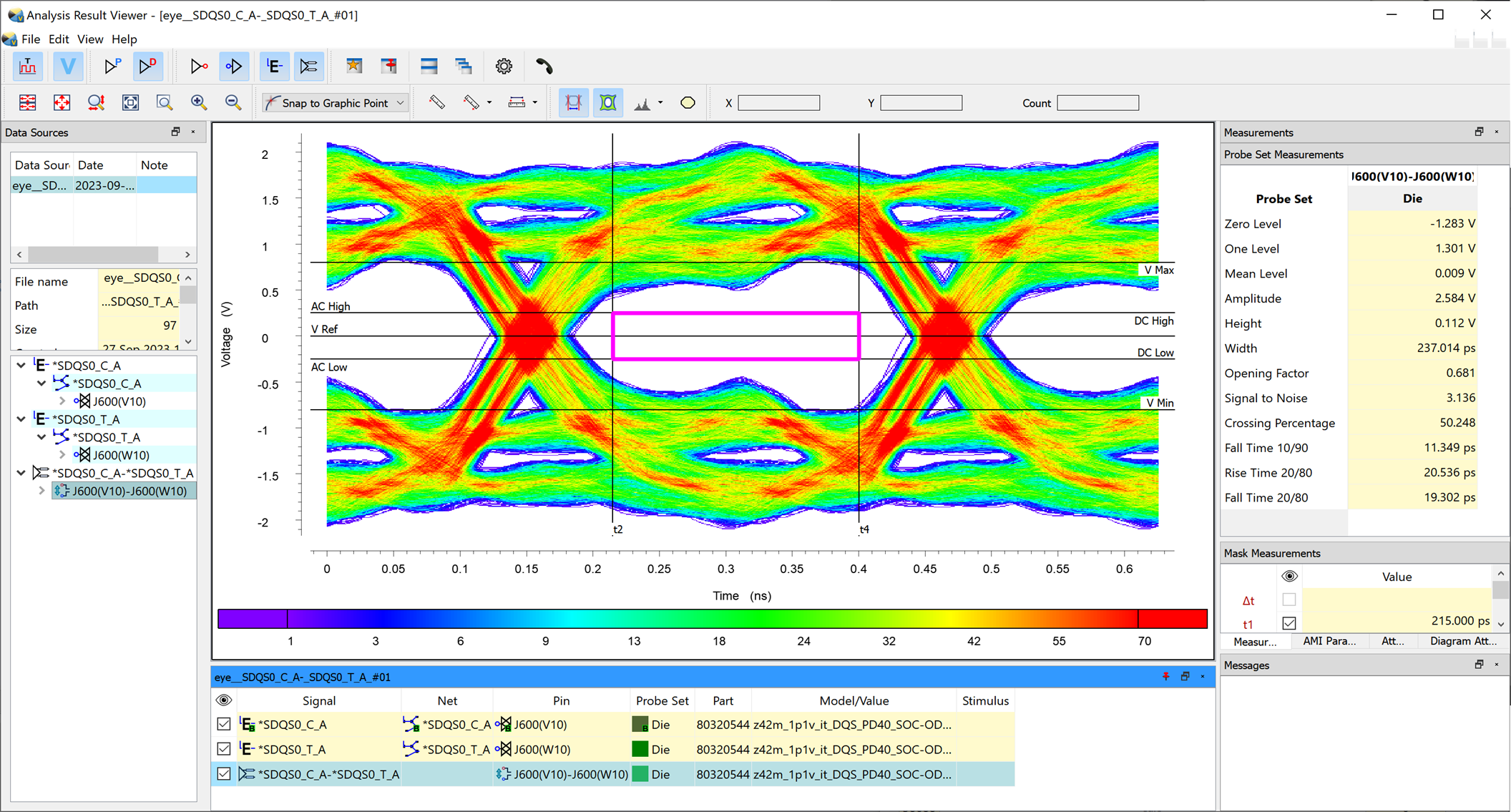

Die komplexen Leiterplatten oder Multi-Board-Systeme von heute erfordern eine detaillierte Planung und Analyse. Mit den Produkten Design Force PI/EMI Advance und SI Advance bietet Ihnen CR-8000 alle Werkzeuge, die Sie zur Planung und Erstellung von Hochgeschwindigkeitsplatinen mit integrierter Signal- und Leistungsintegritätsanalyse benötigen. Darüber hinaus bestehen Integrationen zu den Drittanbietern Ansys und Keysight.

Design Force – SI Advance

Design Force – PI Advance

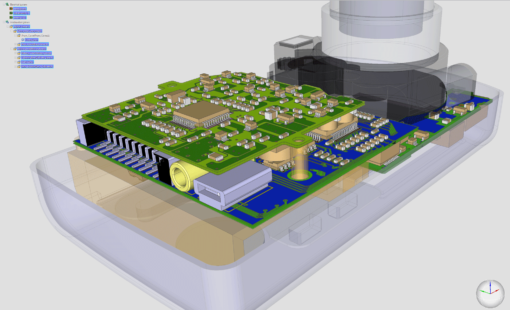

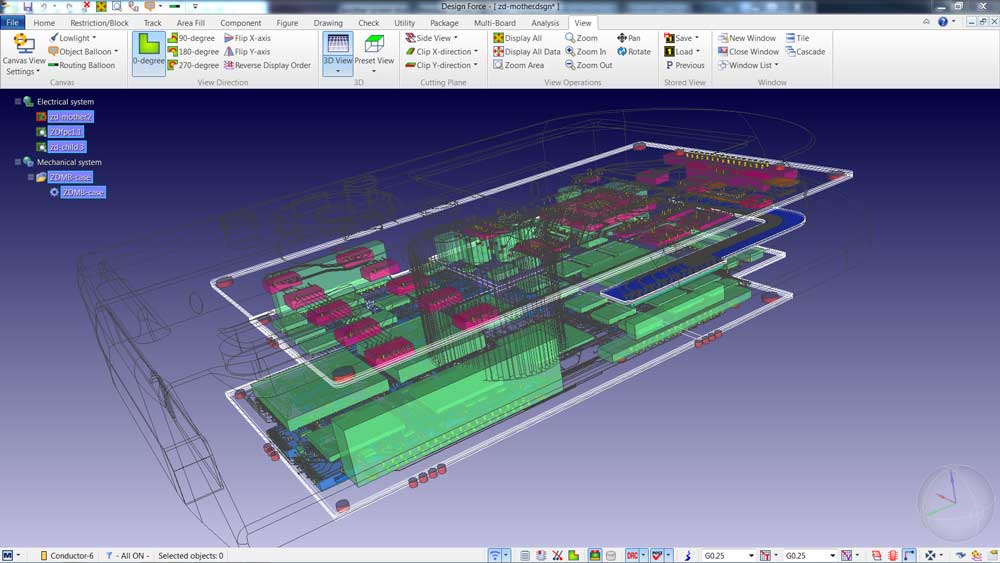

Angesichts der wachsenden Produktkomplexität muss das physikalische Layout einer Leiterplatte im Kontext des gesamten Systems betrachtet werden. Eine PCB-Systemdesignplattform muss Unterstützung für Multi-Board-Design und -Analyse, MCAD-Integration und Kabelbaumdesign bieten. CR-8000 geht darüber hinaus und umfasst das Co-Design von Chip, Package und Leiterplatte.

Mit dem Übergang zu methodischen Ansätzen wie Digital Engineering und Model Based Systems Engineering wird das Arbeiten auf Systemebene immer wichtiger. Teams in der Detailentwicklung müssen künftig an einem System arbeiten, nicht an einer Leiterplatte. CR-8000 bietet alle erforderlichen Funktionen für die Implementierung auf Systemebene.

Design Force

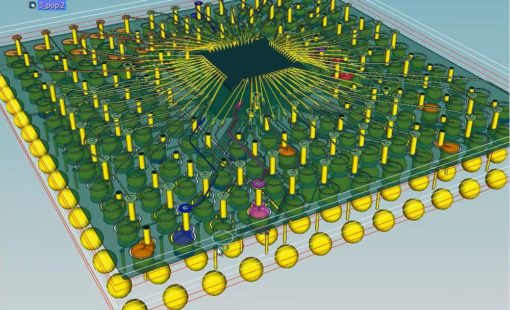

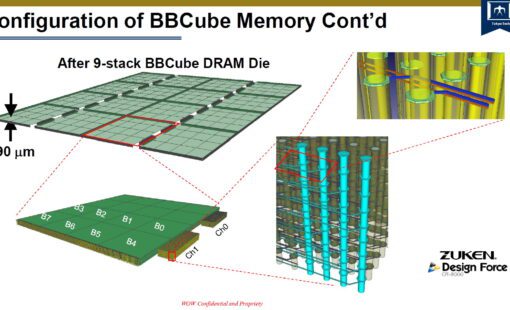

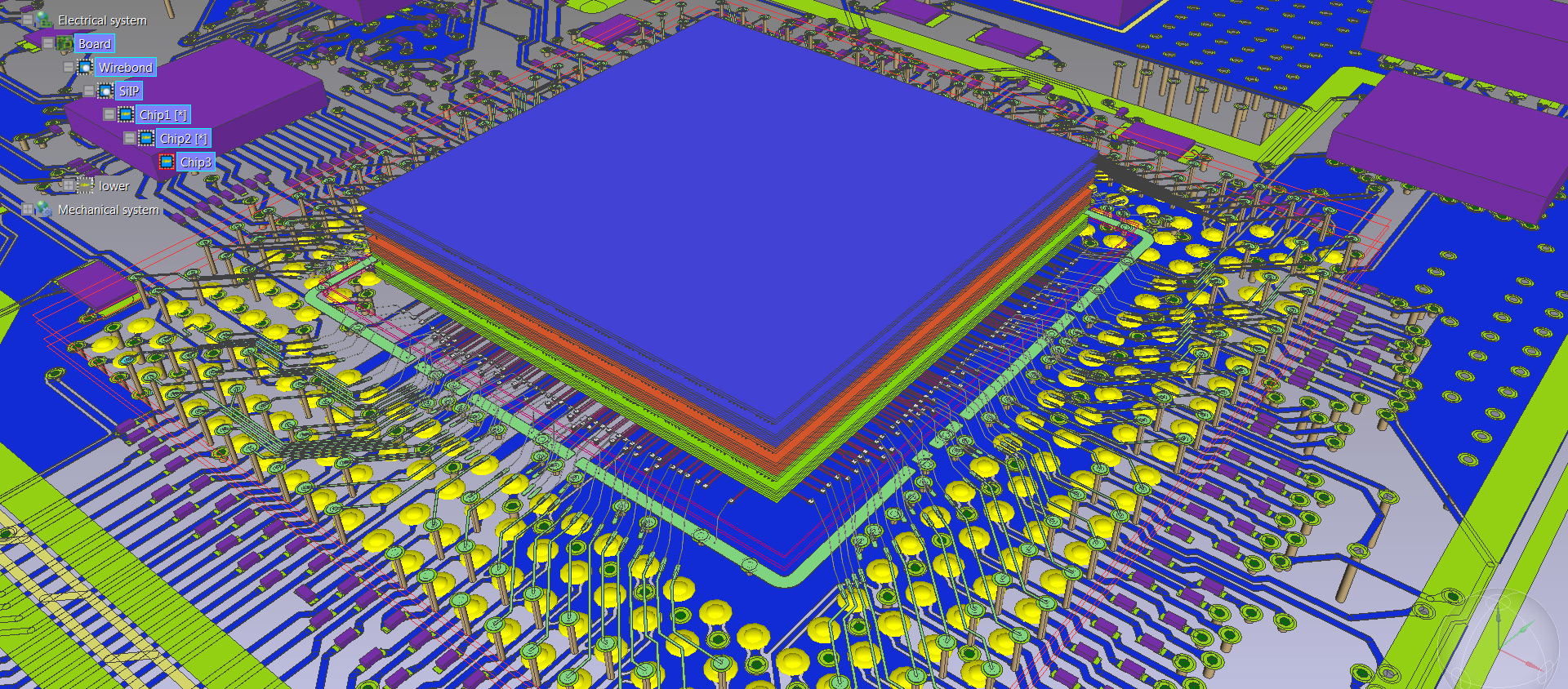

Design Force unterstützt den Entwurf von Single- und Multi-Die-Gehäusen für Wire-Bond-, Flip-Chip- und High-Density Advanced Packaging in einer durchgängigen Umgebung. Designer können ihre Entwürfe mit einer frühen Prototyp-Eingabe von Chip- und Gehäusedaten aus der Bibliothek beginnen, Daten aus IC-Layout-Tools wiederverwenden und die Vorteile parametrischer Assistenten nutzen, um die Erstellung des Systems zu optimieren.

Design Force – IC Package Design

Künstliche Intelligenz (KI) ist eine rasch voranschreitende Technologie im Bereich des PCB-Designs. Unabhängig davon, ob Sie ein erfahrener Designer oder ein Neueinsteiger sind, bietet KI viele Vorteile, die Ihnen das Leben erleichtern können. Sie ist jedoch nicht ohne Herausforderungen. Die einzige Frage, die sich angesichts des technologischen Fortschritts stellt, ist: Sind Sie bereit für die KI-gesteuerte Zukunft des PCB-Designs?

Design Force – KI-gestützte Leiterplattenentwicklung

PLM-Systeme sind in der Regel nicht für die detaillierte Verwaltung der elektronischen Bauteilbibliotheken und Work-in-Process-Daten ausgestattet, die im Leiterplatten-Design erforderlich sind. DS-CR von Zuken ermöglicht die Verwaltung von Work-in-Progress-Daten, die Zusammenarbeit auf Team-Ebene, das Projektmanagement, die Wiederverwendung von Designs, die Rückverfolgbarkeit der Bauteilverwendung (“where-used”) und vieles mehr.

Darüber hinaus sind für DS-CR Integrationen mit führenden PLM-Systemen verfügbar, die Prozesse des Änderungsmanagements oder die Synchronisierung von Bauteilinformationen ermöglichen. Bauteilinformationen können automatisch mit Partnern in der Lieferkette synchronisiert werden.

DS-CR

CR-8000 DFM Center ermöglicht es Entwicklern, die zunehmende Komplexität und Vielfalt heutiger PCBs zu bewältigen und gleichzeitig eine hohe Qualität des Endprodukts und genaue Ergebnisse für die Fertigungsprozesse zu gewährleisten. Mit einer Vielzahl von Funktionen für die Datenaufbereitung und Verifizierung, die die Einhaltung der Fertigungsspezifikationen sicherstellen, erfüllt DFM Center die Anforderungen von modernen Fertigungsprozessen.

DFM Center

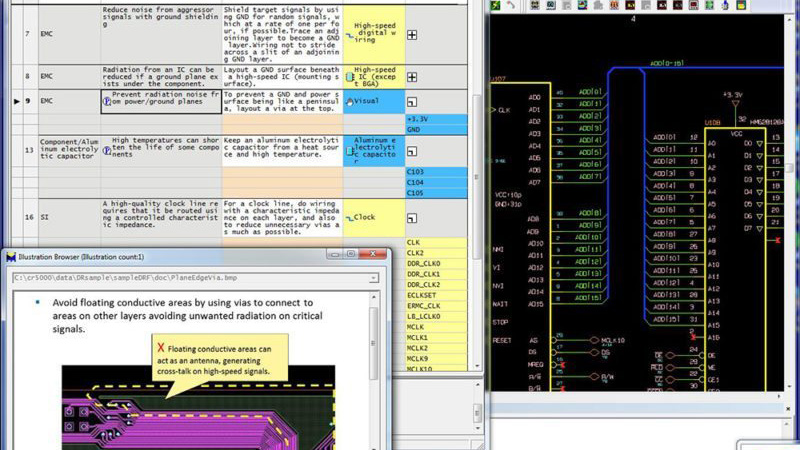

CR-8000 Circuit DR Navi unterstützt Entwicklungsteams bei der Konsolidierung von Fachwissen und Best Practices für das PCB-Layout in einer zentralen Datenbank, die direkt in den Entwicklungsablauf integriert ist. Die umfangreiche Funktionalität von Circuit DR Navi ist besonders geeignet für die Übermittlung von Konstruktionsabsichten sowie für die Unterstützung von neuen Mitgliedern in erfahrenen Entwicklungsteams.

Circuit DR Navi

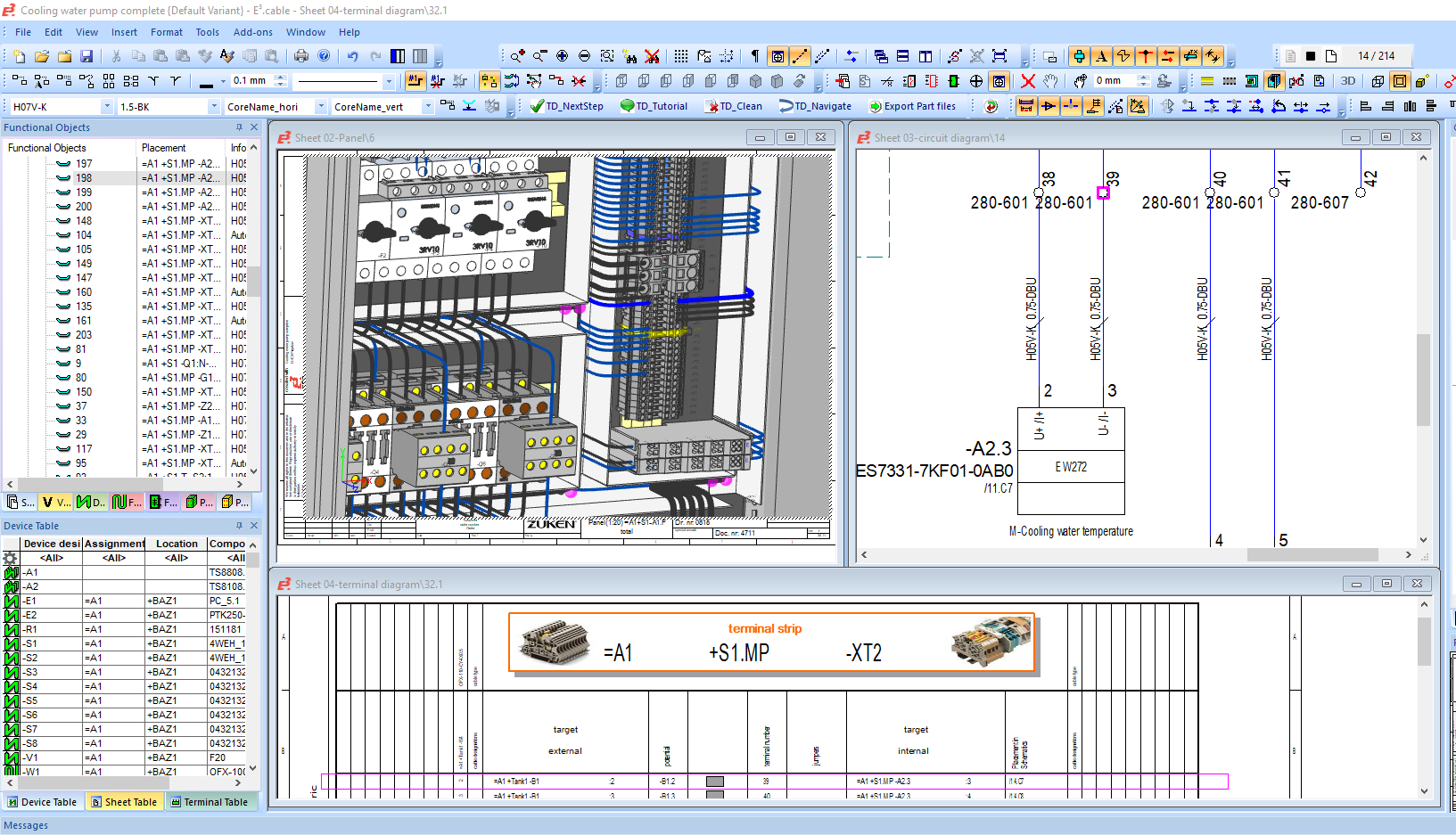

Mit der zunehmenden Komplexität der Produkte ist eine getrennte Entwicklung von elektronischen Baugruppen und Kabelsätzen nicht mehr zeitgemäß. Aus diesem Grund sind die Pin-Zuweisungen des Kabelbaums häufig nicht mit der Leiterplatte synchronisiert. Ein Systemdesign-Ansatz, der Leiterplatte, Kabelbaum und mechanische Umgebung umfasst, verhindert diese häufigen Fehler. Zuken unterstützt in der Kabelsatz-Entwicklung die Leiterplatten-Standardausgabe IPC-2581. E3.series importier IPC-2581 direkt aus CR-8000 in die Kabelbaumentwicklung und trägt dazu bei, Übertragungsfehler zu vermeiden.

E3.series

CR-8000 Produktübersicht

System Planner ist das erste Werkzeug, das ein vollständiges Architekturkonzept von Elektronikprodukten unterstützt. Bislang getrennte Schritte werden intelligent in einer einzigen Applikation zusammengeführt.

Design Gateway ist eine Software für den logischen Schaltungsentwurf und die Verifikation von Ein- und Mehrplatinen-Elektronikdesigns auf Systemebene.

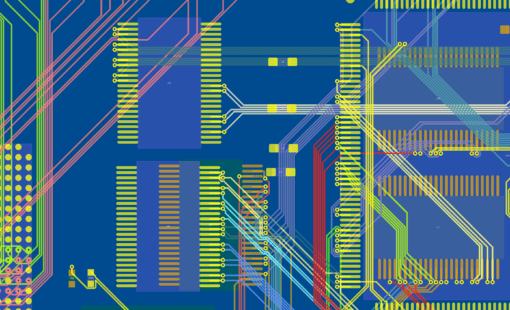

Design Force kombiniert konventionelles 2D-Design mit nativem 3D-Design und den neuesten Technologien in Benutzeroberfläche und Grafik für schnellstes Rendern und Aktualisieren.

Zusätzlich zum Multi-Board PCB Design unterstützt Design Force auch die Entwicklung von IC Packages für Wire-Bond, Flip-Chip und High-Density Advanced Packaging

Mit einem umfangreichen Funktionsspektrum für die Datenaufbereitung und die Verifikation von Fertigungsspezifikationen erfüllt CR-8000 DFM Center die Anforderungen moderner Fertigungsprozesse.

PCB Designdaten-Management. Standortübergreifende Verwaltung von Bibliotheken, Designdaten und Konfigurationen in einer einheitlichen Umgebung

Erfahren Sie mehr über CR-8000

Webinare, Whitepaper, Tech-Tipps & mehr

In diesem Webinar werden die wichtigsten neuen Module und Werkzeuge von CR-8000 anhand des aktuellen Release 2020 vorgestellt und kommentiert.

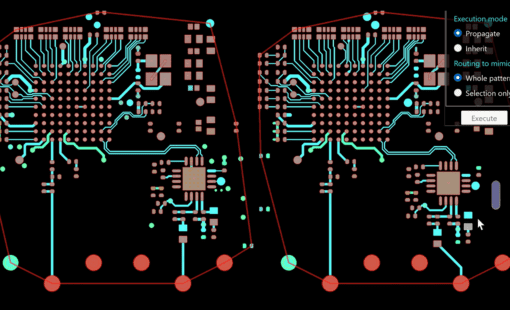

Dieses Webinar wird demonstrieren, wie das Zuken CR-8000 Enterprise PCB Design System Aktualisierungen und Neugestaltungen automatisiert, um auf die Obsoleszenz von Komponenten zu reagieren. Erfahren Sie, wie Sie betroffene Module identifizieren, Designs mit einer schematischen Modulbibliothek aktualisieren und Layout-Änderungen intelligent unterstützen.

This webinar will introduce the use of the Ansys Electronic Database (EDB) format to share information from CR-8000 Design Force to Ansys, the advantages beyond the former ANF-based interface, and how this can help users be more effective and productive.

Dr. Kyle Miller, Leiter des KI-Entwicklungsteams bei Zuken stellt die Autonomous Intelligent Place and Route Software (AIPR) für CR-8000 DesignForce vor.

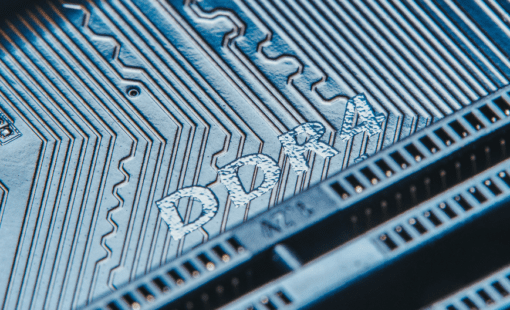

Dieser Vortrag ist keine Einführung in die DDR4-Technologie, sondern zeigt die Vorgehensweise bei der Implementierung von DDR4-Speicherschnittstellen mit Zuken CR-8000 von der Konzeptionsphase bis zur physischen Platzierung und Verlegung sowie der Validierung für SI und PI.

CR-8000 News

Aktuelle Informationen zu CR-8000

Zuken stellt einen innovativen Lösungsansatz für KI-gestütztes PCB-Design vor. Die neue Autonomous Intelligent Place and Route Technologie namens AIPR wird als Teil der erfolgreichen CR-8000 PCB-Engineering- und Design-Plattform von Zuken zum Einsatz kommen.

Zuken helps to overcome design challenges associated with 3D integration in the pursuit of next-generation semiconductor technologies.

Aktuelle CR-8000 Blog Posts

Mit der Veröffentlichung von ChatGPT ist künstliche Intelligenz zu einem Thema geworden, das viele Emotionen ausgelöst hat. In unserem Blog gehen wir der Frage nach, ob KI zur Unterstützung von Zukens Kerngeschäft, der Lösung komplexer Designherausforderungen wie PCB-Layout und Routing, eingesetzt werden könnte.

Die derzeit weit verbreitete DDR4 Speichertechnologie stellt in der aktuellen Technologielandschaft oft eine schwierige Herausforderung im Designprozess einer elektronischen Anwendung dar. Finden Sie heraus, was zu beachten ist.

Das komplexe Zusammenspiel von elektrischen, mechanischen und thermischen Aspekten erfordert die Berücksichtigung von Signalintegrität und Stromverteilung bei gleichzeitiger Beachtung von produktionsbedingten Parametern. So hilft CR-8000 Design Force beim PCB-Design.

In unserem neuen Blogbeitrag tauchen wir in die faszinierende Welt des KI-gestützten PCB-Designs ein und beleuchten die Vorteile und Einschränkungen und stellen die Place and Route Lösung vor, an der Zuken arbeitet.

Das PCB-Design bildet seit Jahrzehnten das Herzstück elektronischer Innovation. Mit dem unaufhaltsamen Fortschritt der Technologie ergeben sich jedoch kontinuierlich neue, anspruchsvollere Herausforderungen. Wir zeigen Ihnen, wie Sie diesen erfolgreich begegnen können.

Mit dem Release 2023 von CR-8000 wird der Aufwand für die Wiederverwendung bestehender Designs im Engineering-Frontend Design Gateway sowie in den Layout- und Routing-Anwendungen von Design Force erheblich reduziert.