Eine einheitliche Umgebung für die Bearbeitung von Chip-Scale-Packaging (CSP), Multi-Chip-Modulen (MCMs) und Systems-in-Package (SiP)

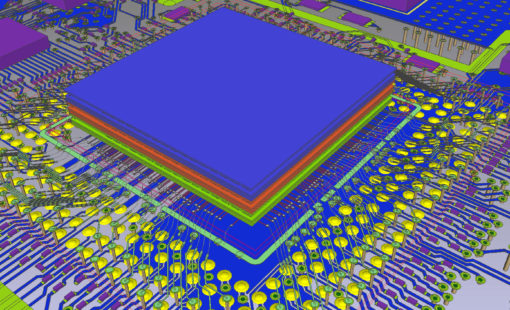

Design Force bietet eine intuitive, integrierte Umgebung für die Entwicklung von Single- und Multi-Chip-Modulen für Wire-Bond, Flip-Chip und High-Density Advanced Packaging. Konstrukteure können Ihre Arbeit frühzeitig mit dem Einlesen von Chip- und Gehäusedaten aus der Bibliothek beginnen, sie können Daten aus IC-Layoutwerkzeugen wiederverwenden und sie können die Vorteile der parametergestützten Assistenten nutzen, um die Erstellung des Systems zu rationalisieren.

Eine einheitliche Umgebung für die Bearbeitung von Chip-Scale-Packaging (CSP), Multi-Chip-Modulen (MCMs) und Systems-in-Package (SiP)

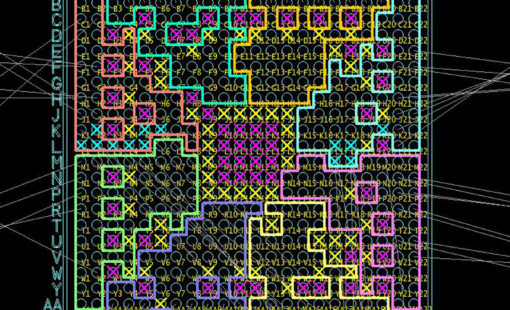

Automatisierte Ball-Grid Pinbelegung mit der Fähigkeit, komplexe Entflechtungsmuster zu optimieren

Machbarkeitsstudien mit erweiterten Fan-Out/Fan-In und Autorouting-Funktionen zur Optimierung der Anzahl von Package Layern

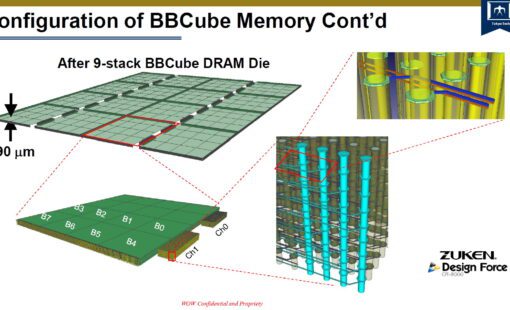

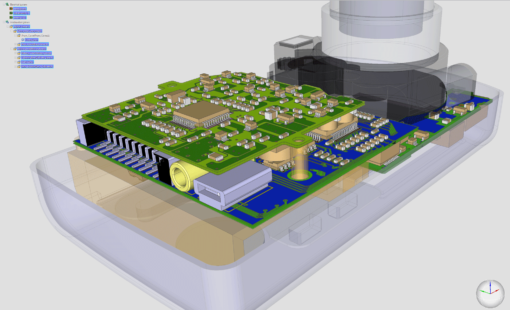

2D/3D-Stacking-Strukturen könne in jeder Konfiguration bearbeitet werden: gestapelt, benachbart, Zwischenlagen (Interposer), oder als Wire-Bond und Flex-Chip-Packages

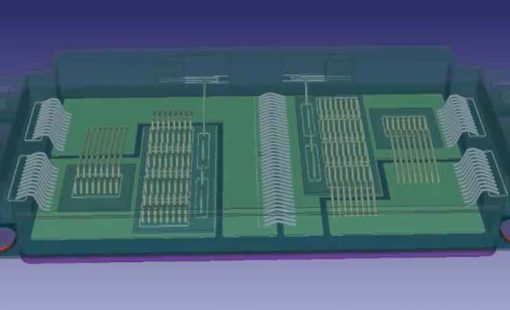

Mit der nativen 3D-Plattform von Design Force können dicht gepackte Verbindungsstrukturen für Wire-Bond oder Flex-Chip-Packages einfach und sicher implementiert und verwaltet werden, so dass mit der Embedded-Component-Technologie fortschrittliche Packaging und Moduldesign realisiert werden können.

Die Flip-Chip-Methode wird häufig für Designs mit hoher I/O-Zahl verwendet. Diese Methode reduziert die Induktivität erheblich, ermöglicht hohe Signalgeschwindigkeiten und verfügt über bessere Wärmeleiteigenschaften.

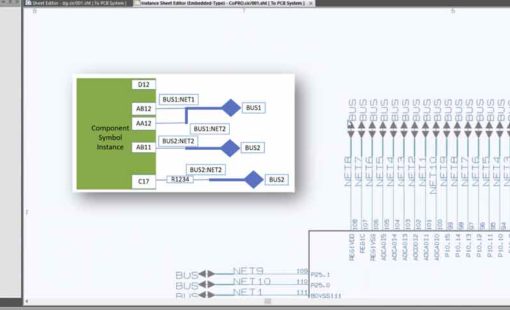

Redistribution Layers (RDL) werden verwendet, um I/O-Pads mit Lötpunkten zu verbinden. Probleme mit RDLs entstehen, wenn eine einzelne Schicht trotz manuellem Routing nicht ausreicht, um das Routing für ein großes Design abzuschließen, da die Platzierung der Ein- und Ausgänge nicht optimal ist. Daher ist in Systemen mit mehreren Die-Packages und Flip-Chips das Routing Redistribution Layer (RDL) der Schlüssel zu optimalen Packaging.

Um ein leistungsfähiges und kosteneffizientes Chip-Package-Board-System zu realisieren, ist eine frühzeitige Machbarkeitsanalyse unerlässlich. Nur so können physikalische Randbedingungen an die elektrischen Anforderungen angepasst werden. Die physikalischen Beschränkungen (Constraints) werden genutzt, um die Gesamtlänge der RDL-Leitungen zu minimieren, während die elektrischen Anforderungen verwendet werden, um ein korrektes Verhältnis von Signalleistung, geringen Stromverbrauch, reduzierter Induktivität und geringeren thermischen Effekten sicherzustelle

Konstrukteure können eine breite Palette interaktiver und automatischer Routingtools nutzen, um den Aufwand für die Durchführung des Fan-in/Fan-out-Routings, der automatischen Ball-Grid-Zuweisungen auf dem Package und des Routings zu reduzieren.

Design Force Advanced Packaging unterstützt die Integration von Best-in-Class-Tools von Partnern wie ANSYS, AWR, Agilent und Synopsys für RF, Full Wave FD/TD, Power Integrity sowie thermische Extraktion und Analyse. Design Force beinhaltet auch eine native EMI-, Signal- und Spannungsintegritätsanalyse zur Vermeidung von Konstruktionsfehlern.

Design Force Advanced Packaging enthält eine Reihe von Dienstprogrammen und Assistenten, die dabei helfen, Wire-Bond-Profile, Bond-Pad-Platzierung, Multi-Die- oder Bond-Pad-Verbindungen zu definieren und das Stacking von IC Packages mit Online-Design und Manufacturing-Regelprüfungen zu verwalten.

Zugehörige Ressourcen

Zuken helps to overcome design challenges associated with 3D integration in the pursuit of next-generation semiconductor technologies.

Der typische Entwurfsablauf für ein Power-Modul erfolgt in MCAD, wo nur eine Strukturanalyse möglich ist. Der Wechsel zu einem neuen Entwurfsablauf mit CR-8000 Design Force ermöglicht auch eine elektrische Analyse. In diesem Webinar lernen Sie die Funktionen und Vorteile dieses neuen Verfahrens kennen.

Schwerpunkte bei der Entwicklung des CR-8000 2020 waren die Steigerung der Designeffizienz, die Bereitstellung umfassender Design- und Verifikationsmöglichkeiten auf Systemebene sowie die Unterstützung der jüngsten Fortschritte in der Hardware-Packaging-Technologie.

Zugehörige CR-8000 Produkte

Zusätzlich zu den hochentwickelten Funktionen für das PCB-Layout bietet Design Force die Möglichkeit des Co-Designs von Chips, Gehäusen und Leiterplatten, so dass ein hierarchisches 3D-Design in Echtzeit ermöglicht wird.

Der Graphical Pin Manager von CR-8000 bietet eine effektive FPGA/PCB Co-Design-Umgebung für die neuesten Bauelemente von Anbietern wie Xilinx, Intel, Lattice und Microsemi.

Design Force kombiniert konventionelles 2D-Design mit nativem 3D-Design und den neuesten Technologien in Benutzeroberfläche und Grafik für schnellstes Rendern und Aktualisieren.