22. Mai 2019 – Westford, MA, USA – Zuken arbeitet mit dem Center for Heterogeneous Integration and Performance Scaling (CHIPS), einem gemeinschaftlichen akademischen/ industriellen Forschungsvorhaben der Univesity of California (UCLA) zusammen. Ziel des Projektes ist es, Lösungen für die Herausforderungen zu entwickeln, die mit dem wachsenden Bedarf an Rechenleistung in heterogenen Computing-Umgebungen einhergehen.

Das UCLA CHIPS-Konsortium besteht aus Industriepartnern von Rohstofflieferanten, Equipment-Herstellern, Halbleiterherstellern und Systemintegratoren. Es wird von Universitäten, Regierungsbehörden und Industriekonsortien unterstützt und arbeitet gemeinsam an der Entwicklung neuer Packaging-Technologien und Systemarchitekturen sowie der Nachwuchsförderung.

Zuken unterstützt das Team von UCLA CHIPS dabei, die System-Level-Designfunktionen von CR-8000 für das Layout und die Optimierung von Verbindungsstrukturen zwischen ungehäusten Dies auf Substratebene zu nutzen. Darüber hinaus wird CR-8000 Design Force im Rahmen der technischen Ausbildung eingesetzt, um die Studenten in der Entwicklung von Lösungen für High-Speed-Problemstellungen zu schulen.

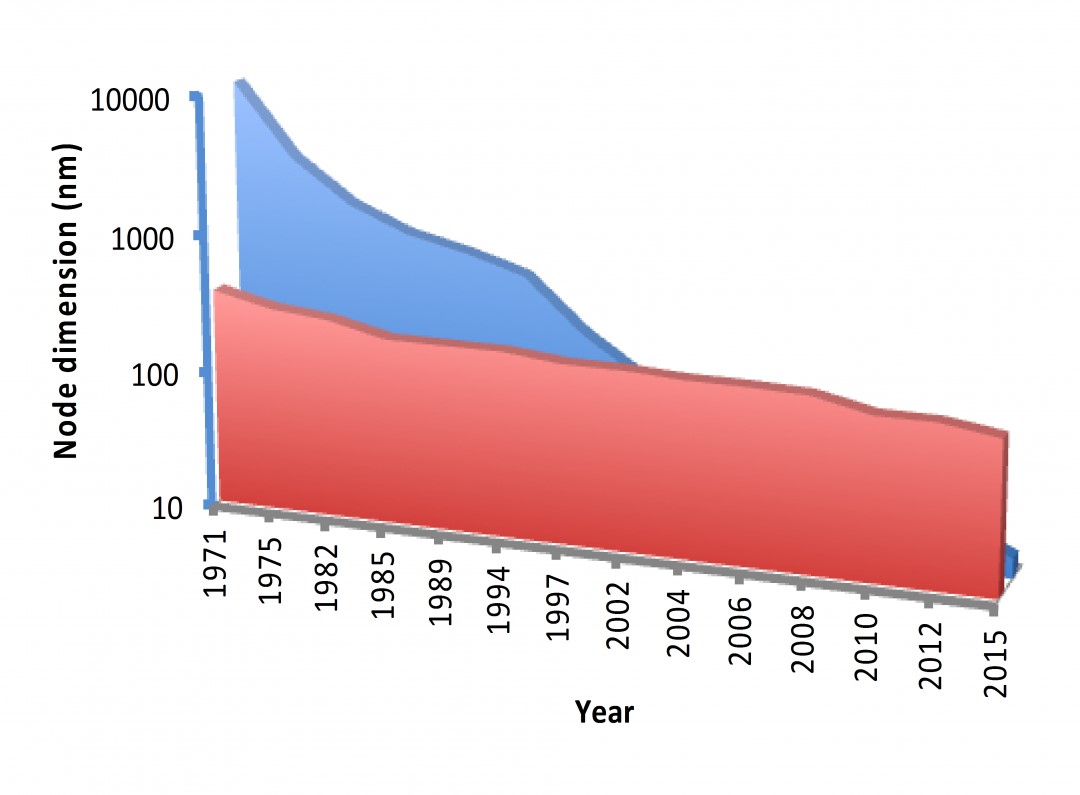

„Die klassische CMOS-Skalierung hat in den letzten Jahrzehnten eine 3000-fache Reduzierung der Featuregröße erreicht”, erklärt Prof. Subramanian S. Iyer, Distinguished Professor an der UCLA Electrical and Computer Engineering und Direktor von UCLA CHIPS. „Obwohl diese Entwicklung noch nicht abgeschlossen ist, steigen die Entwicklungs- und Herstellungskosten dramatisch an. Dabei konnten andere Aspekte des Systems wie die Gehäuse- und Platinenminiaturisierung nicht Schritt halten, während der Aufwand für die Integration von immer mehr und immer vielfältigeren Funktionen in einen System-on-Chip-Ansatz exponentiell ansteigt.”

Der Ansatz von UCLA CHIPS geht daher über die SOC-Integration auf Systemebene hinaus: „Bei CHIPS konzentrieren wir uns auf Packaging- und Integrationsverfahren auf Systemebene, um die Gesamtsystemleistung zu verbessern, anstatt die einzelnen Systemkomponenten zu verbessern”, sagt Prof. Iyer.

Das Ziel: Ein Moore’s Gesetz für Packaging-Formen auf den Weg bringen

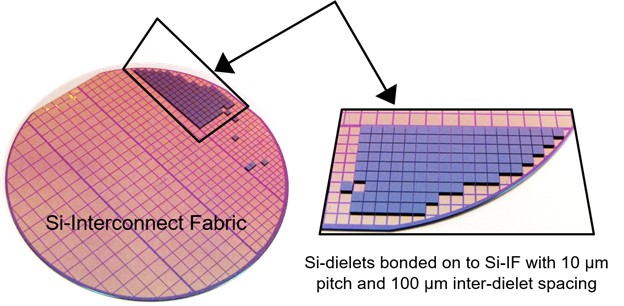

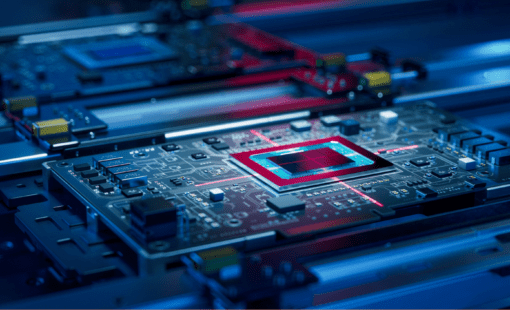

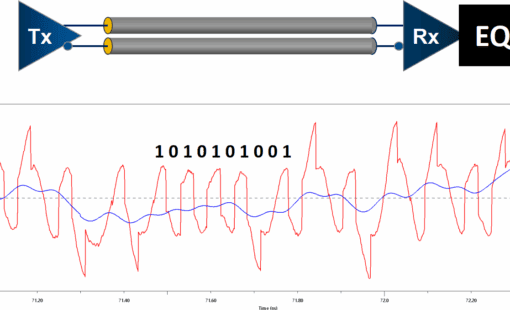

UCLA CHIPS hat als Pionier das Konzept der Integration kleiner Dielets direkt auf einem siliziumbasierten Interconnect Fabric (Si IF) oder einem flexiblen Fan-out Wafer-Level Package (FlexTrate*) entwickelt. Dies ermöglicht eine extrem hohe Integration von verschiedenen Dies, was wiederum die Realisierung eines heterogenen Systems auf dem Wafer ermöglicht. Auf diese Weise können wir das Package deutlich skalieren – und eine Art Moore’s Law für Verpackungen ermöglichen. Die Inter-Die-Verbindungen können von BGA-Abständen von mehreren hundert Mikrometern bis zu einigen Mikrometern skaliert werden, und der Inter-Die-Abstand kann auf 20 µm reduziert werden. Dies ermöglicht deutliche Verbesserungen in Bezug auf Latenzzeiten, Bandbreiten und Energieverbrauch pro Bit gegenüber herkömmlichen Packaging-Methoden.

Durch seine Fähigkeit, komplexe Designs auf Systemebene in 2D und 3D zu modellieren und zu layouten, ist Zukens CR-8000 Elektronikdesignumgebung ideal geeignet, um die komplexen Die Stack-ups und Interposer-Designs zu modellieren, die für die Verfahren des Silicon Interconnect Fabric und FlexTrate erforderlich sind. Im Rahmen seines Engagements, mit Kunden an der Erforschung neuer Lösungsansätze zu arbeiten, stellt Zuken Design-Tools und Dienstleistungen für die Forschung im Rahmen der CHIPS-Initiative sowie für die Ausbildung des akademischen Nachwuses an der UCLA zur Verfügung.

Abgestimmte Lösungen für komplexe Anforderungen

Humair Mandavia, Chief Strategy Officer und Leiter des Zuken SOZO Center in San Jose, CA, kommentiert: “Unser F&E-Team in San Jose wurde eingerichtet, um enger mit unseren Kunden und Partnern im Silicon Valley und in den USA zusammenzuarbeiten und ihnen dabei zu helfen, neue Technologien und Methoden für das Hardware-Design zu entwickeln. Unsere Partnerschaft mit UCLA CHIPS ist ein weiteres Beispiel für diesen Ansatz, der für Zuken und unsere Kunden gleichermaßen fruchtbar ist: Wir sind damit in der idealen Position, um zeitnah und zielgerichtet Lösungen für die immer komplexeren Anforderungen der heutigen Produktentwicklung anbieten zu können.” Weitere Informationen: https://chips.ucla.edu/

– Ende –

* FlexTrate

FlexTrateTM verwendet biokompatibles Polydimethylsiloxan (PDMS) als Packaging und Mold-Material im Fan-Out Wafer Level Packaging (FOWLP). Dieses Verfahren bietet aufgrund seiner niedrigeren Glasumwandlungstemperatur und der Young-Modulwerte einen erheblichen Vorteil bei der Reduzierung von Die-Shift und Wafer-Verzug im Vergleich zu herkömmlichen Epoxy-basierten Mold-Materialien (EMC). Die CHIPS FlexTrateTM-Plattform ist auch ein Schlüsselfaktor für die heterogene Integration auf flexiblen Substraten, bei der heterogene Dies auf einem flexiblen Substrat dicht beieinander integriert und über Prozesse auf Wafer-Ebene miteinander verbunden werden..

Quelle: https://chips.ucla.edu/research/project/5

Pressetext und Bildmaterial kann hier heruntergeladen werden