Regelbasierte Layout-Adviser für schnelle EMC-Prüfungen

Mit steigenden Datenraten und immer engeren Designmargen bleibt im PCB-Design kaum Raum für Trial-and-Error. Schon kleine Änderungen in Impedanz, Rückstromführung oder PDN-Verhalten können eine High-Speed-Schnittstelle aus dem Tritt bringen – lange bevor der erste Prototyp im Labor liegt. Deshalb sind Simulation und Analyse unverzichtbar. Sie machen Signalverzerrungen, Schwächen in der Stromversorgung und potenzielle EMI-Risiken früh sichtbar, sodass sich Probleme rechtzeitig beheben lassen und teure Redesigns oder Compliance-Überraschungen entfallen.

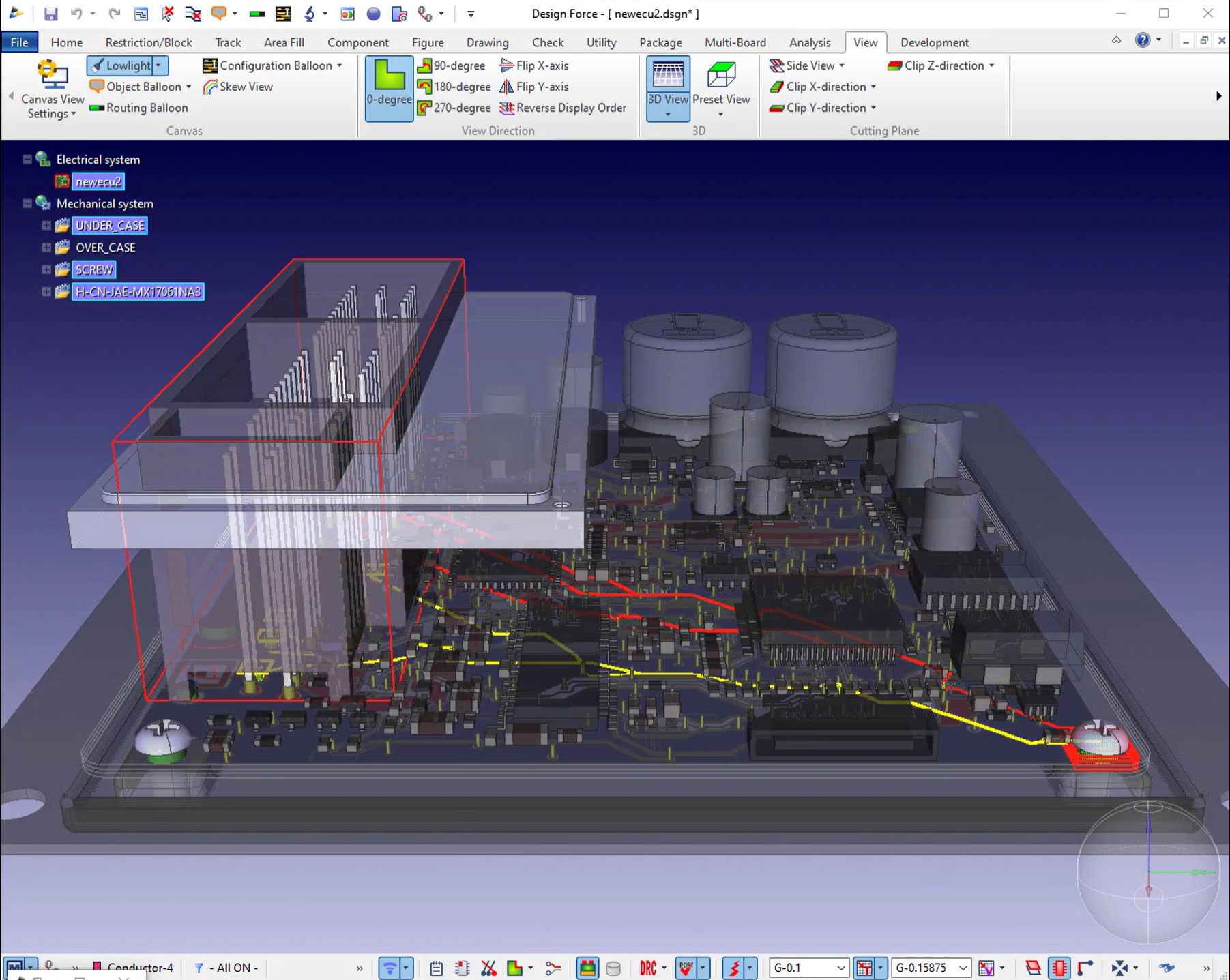

Die in Zukens CR-8000 integrierte Simulationssuite setzt genau hier an. Sie vereint Signal- und Power-Integrity-Analysen sowie EMI-Bewertungen direkt im Designprozess. Ingenieure können Lagenaufbauten, Routing-Strategien, differenzielle Paare, PDN-Verhalten, Übersprechen und Eye-Diagramme bereits während der Layoutphase beurteilen. Dieser durchgängige Ansatz reduziert Redesigns, verbessert die Zuverlässigkeit von High-Speed-Schnittstellen und unterstützt dabei, Leistungs- und Compliance-Ziele bereits beim ersten Anlauf zu erreichen.

Mit einem umfassenden Angebot integrierter Anwendungen bietet CR-8000 eine durchgängige Umgebung zur Simulation und Analyse Ihrer Leiterplattendesigns. Ob Single-Board- oder Multi-Board-Projekt, die Plattform stellt alles bereit, was Sie zur Sicherung der elektrischen Integrität und Zuverlässigkeit Ihrer PCB-Entwürfe benötigen.

Regelbasierte Layout-Adviser für schnelle EMC-Prüfungen

Integrierte Signal-Integrity-Analysefunktionen

Layout-begleitende Power-Integrity-Analyse und EMV-Prüfung

Eine einheitliche Analyseumgebung für das Signal- und Emissionsverhalten von PCB-Designs

EMC Adviser EX bietet gezielte Hilfe für die Bewertung der elektromagnetischen Verträglichkeit eines PCB-Designs. Das Tool macht Layout-Entscheidungen sichtbar, die Emissionen erhöhen oder die Störfestigkeit verringern können, indem es Rückstrompfade, Ebenenunterbrechungen, hoch-dI/dt-Leitungen und antennenartige Strukturen analysiert. Es markiert kritische Bereiche, bewertet EMC-Risiken und empfiehlt geeignete Korrekturmaßnahmen, solange das Layout noch flexibel ist. Durch diese praxisnahe, layoutbewusste Unterstützung in einer frühen Phase hilft EMC Adviser EX, späte Compliance-Probleme zu vermeiden und die EMC-Robustheit des Designs nachhaltig zu erhöhen.

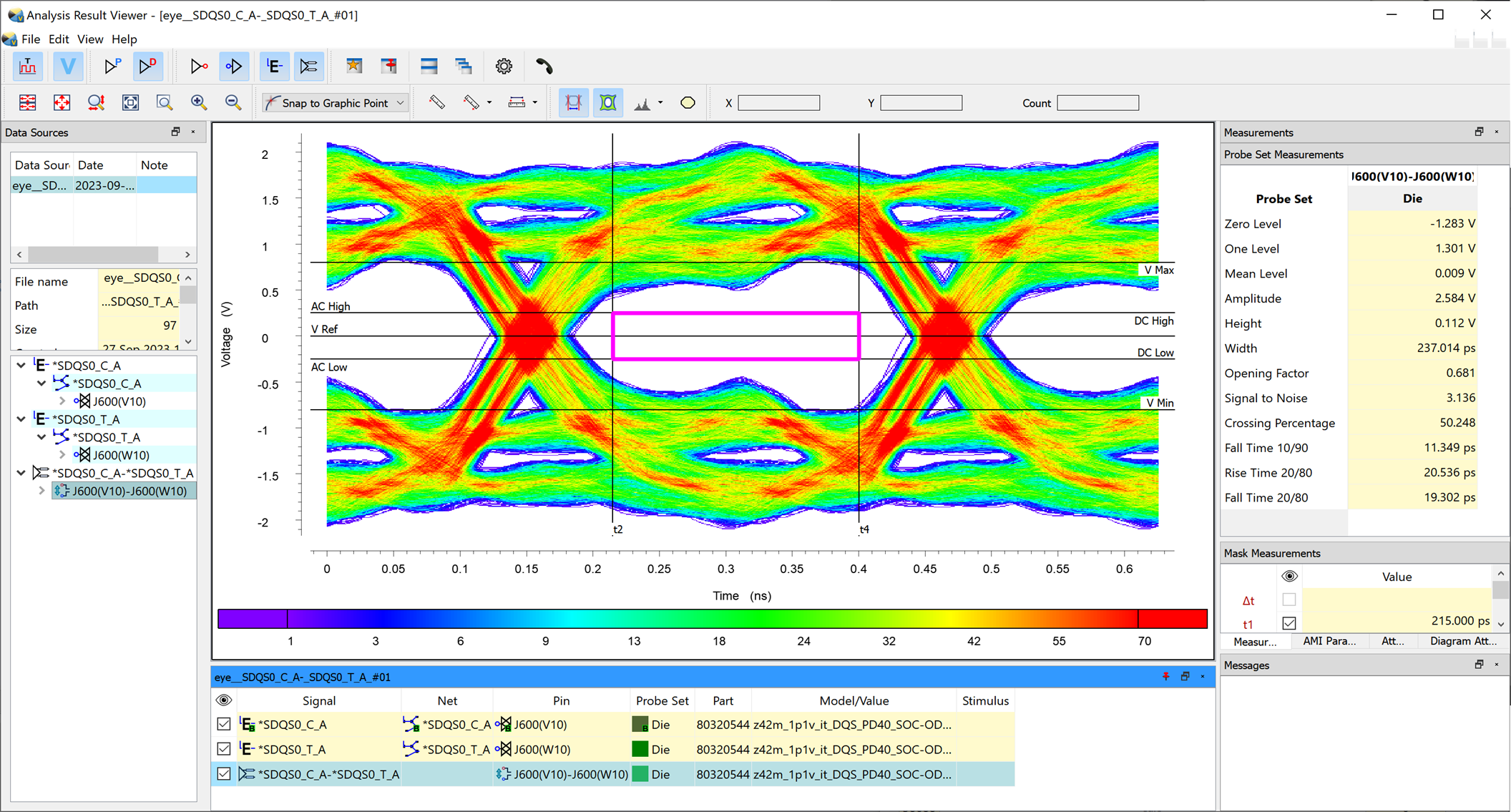

Design Force SI Advance bündelt umfangreiche Signal-Integrity-Analysefunktionen in einem integrierten Paket und gibt Entwicklern damit einen deutlich besseren Einblick in das Hochgeschwindigkeitsverhalten ihres Designs. Die Lösung umfasst feldlöserbasierte Impedanzextraktion sowie Zeit- und Frequenzbereichssimulationen, um Reflexionen, Dämpfung und Rückstrompfade realistisch zu bewerten. Eine Übersprechenanalyse erkennt Kopplungsrisiken frühzeitig. Topologie-Untersuchungen unterstützen verschiedene Routingstrategien, und IBIS-AMI-Modelle ermöglichen eine praxisnahe Analyse von SerDes-Kanälen, einschließlich Jitter- und Eye-Diagramm-Bewertung. Zusammen bieten diese Funktionen eine umfassende Sicht auf das SI-Verhalten und erhöhen die Chance auf verlässliche Ergebnisse bereits im ersten Design-Durchlauf.

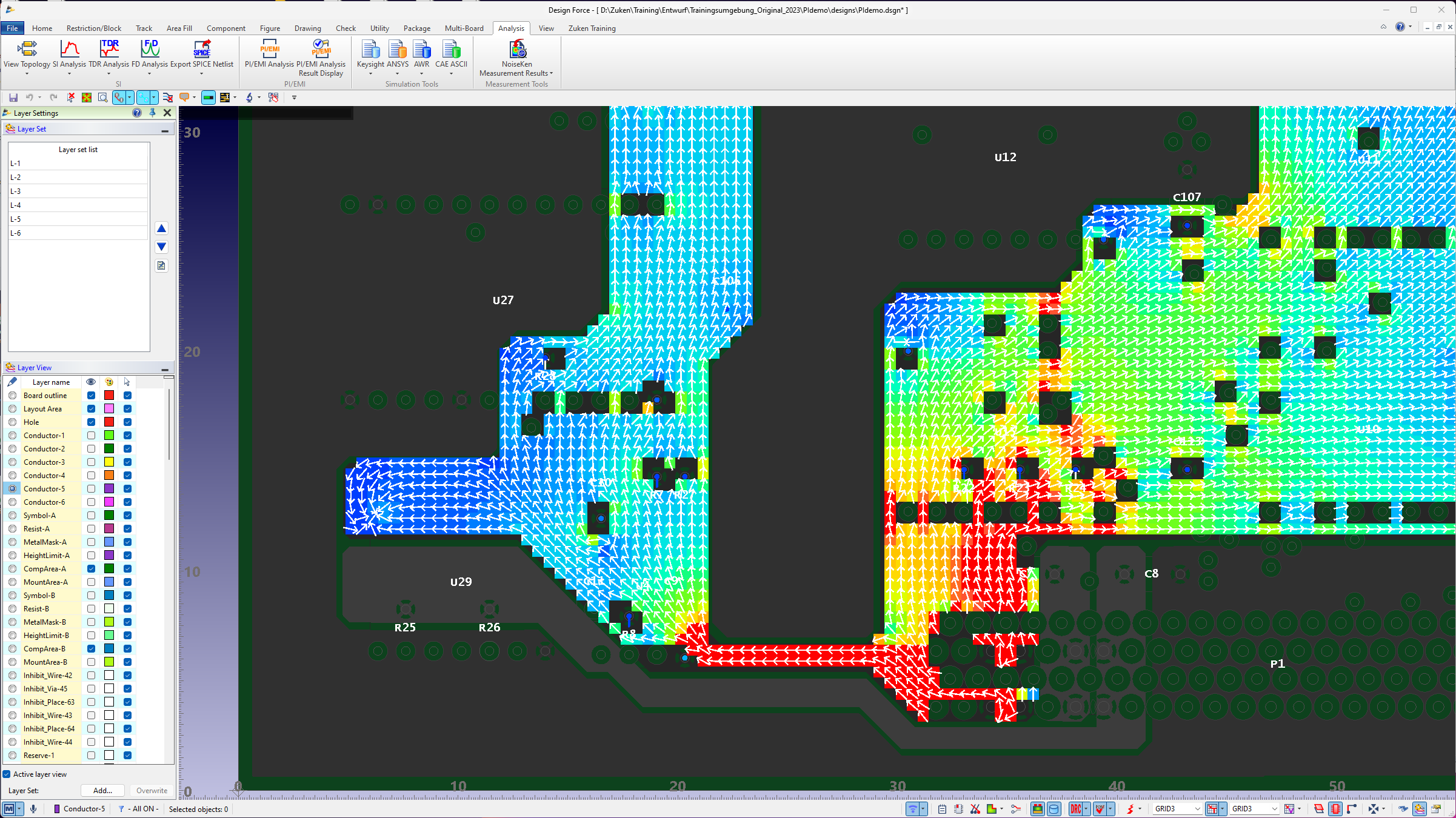

Design Force PI/EMI Advance bietet umfassende Power-Integrity- und EMI-Analysen direkt in der Layoutumgebung. Die PI-Engine bewertet das Verhalten des PDN, zeigt Spannungsabfälle, Transienten und die Wirksamkeit der Entkopplung auf und sorgt so für stabile Versorgungsschienen. Die EMI-Analyse liefert schnelle Abschätzungen zu Worst-Case-Emissionen und berücksichtigt dabei die Leiterplatte ebenso wie angeschlossene Kabel und Kühlkörper. Sowohl Gleichtakt- als auch Gegentaktstrahlung werden einbezogen. Dies verschafft frühzeitig verwertbare Einblicke in die Robustheit des PDN und das elektromagnetische Verhalten des Designs.

Webinare zum Thema

Dieser Vortrag ist keine Einführung in die DDR4-Technologie, sondern zeigt die Vorgehensweise bei der Implementierung von DDR4-Speicherschnittstellen mit Zuken CR-8000 von der Konzeptionsphase bis zur physischen Platzierung und Verlegung sowie der Validierung für SI und PI.

Aktuelle Blogs zum Thema

High-Speed-Serial-Links wirken oft wie schwarze Magie – steigende Datenraten verstärken dieses Gefühl. Donald Telian (SI Guys) und Ralf Brüning holen die Diskussion zurück zu den Grundlagen.

To keep a good high-speed signal quality from driver to receiver on a PCB is not an easy task for designers. One of the most challenging issues is managing the propagation delay and relative time delay mismatches. Let me take you through the process...

Wussten Sie, dass der Ausdruck "Übersprechen" (engl. Crosstalk) aus der Zeit der Telefonzentralen stammt, in denen Mitarbeiter Anrufer miteinander verbunden haben, die manchmal ungewollt das Gespräch eines anderen hören konnten? Man sprach im wahrsten Sinne des Wortes über eine andere Leitung hinweg.

In part 1 of this blog we took a back-to-basics approach and discussed line impedance and its effects in signal integrity. As every electrical conductor comprises capacitance, an inductance, and a frequency-dependent ohmic resistance, and with increasing frequencies, these electrical characteristics will influence and distort the signal.

Impedance and impedance control belong to the oldest and most often discussed topics in PCB design. They are especially important with the high-speed design when related to signal integrity. In this, the first of a two-part blog, we’ll go back to the basics of impedance/impedance control and consider what influences line impedance. In part two, we’ll set about controlling it.

Tips for when routing differential pairs - You can tell when something isn’t as clear as it should be. The same questions come up time and again. You ask three experts and get three different answers. Routing differential pairs can be like that. Why? Because “it depends” - on exactly what signals those pairs are carrying and what kind of PCB you’re creating.