Höhere Design-Qualität für High-Speed-Schaltungen durch frühzeitige Absicherung kritischer Signale, reduzierte Iterationen und robuste, vorhersagbare Layoutstrukturen.

Moderne Elektronik arbeitet mit hohen Datenraten, dichten Multilayer-Strukturen und strengen EMV-Anforderungen. Dadurch steigt der Bedarf an Layouts, die Signalintegrität und elektromagnetische Verträglichkeit schon früh absichern. EMC Adviser EX erkennt kritische Effekte bereits im Designprozess und unterstützt Sie dabei, Störungen gezielt zu vermeiden. Die Lösung zeigt Impedanzänderungen, Rückstromunterbrechungen, Übersprechen und Schwächen im Power Distribution Network klar auf. So entwickeln Sie robuste Leiterplatten, die funktionale und regulatorische Vorgaben sicher erfüllen.

Höhere Design-Qualität für High-Speed-Schaltungen durch frühzeitige Absicherung kritischer Signale, reduzierte Iterationen und robuste, vorhersagbare Layoutstrukturen.

Unterstützung von Routing-Entscheidungen mithilfe konsolidierter SI/PI/EMV-Constraints für Leiterbahnführung, Via-Strategien und PDN-Topologien

Erkennen von EMV-kritischen Effekten wie parasitären Antennen, unterbrochenen Rückstrompfaden, Impedanzverschiebungen und stark koppelnden Geometrien.

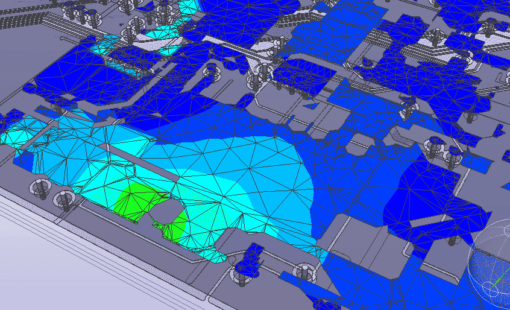

EMC Adviser EX analysiert Ihr Design auf Effekte wie parasitäre Antennen, Abschirmungslücken, unterbrochene Rückstrompfade, Impedanzänderungen und stark koppelnde Geometrien. Diese Prüfungen helfen Ihnen, Strukturen zu erkennen, die Emissionen erzeugen, Jitter verursachen oder mit steigenden Datenraten die Störabstände reduzieren.

Der Regelkatalog umfasst SI-, Power-Integrity- und EMV-Aspekte und verschafft Ihnen frühzeitig Transparenz über Layout-Risiken. Indem Routingmuster, Lagenwechsel und Entscheidungen in der Stromversorgungsstruktur identifiziert werden, die unerwünschte Abstrahlung oder Signalintegritätsprobleme hervorrufen, unterstützt Sie das Tool dabei, sauberere, robustere High-Speed-Designs zu realisieren, ohne Ihren Workflow zu verkomplizieren.

Neue Regeln für Strahlungsimmunität und stabile Masseanbindung erweitern den 3D EMC Advisor über eine rein emissionsorientierte Analyse hinaus, indem sie sichtbar machen, wie externe Felder und Erdungsstrukturen mit der Leiterplatte innerhalb ihres mechanischen Gehäuses interagieren.

Durch die Visualisierung des Eindringens externer Strahlung, des Verhaltens von Massepfaden und der elektromechanischen Bedingungen, die die Störanfälligkeit erhöhen, liefert das Tool frühzeitig Einblicke in Immunitätsrisiken, die in herkömmlichen Analyseabläufen nicht erkennbar werden.

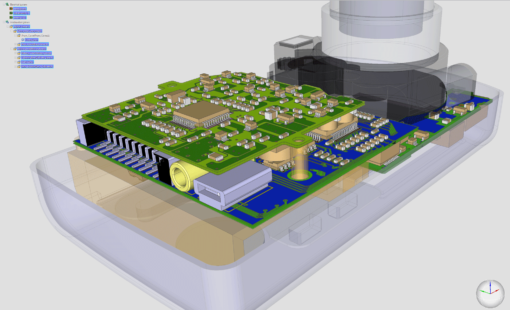

EMC Adviser EX bietet Analysen, die über klassische Leiterplattenprüfungen hinausgehen, indem das elektrische Verhalten mit dem 3D-mechanischen Kontext des Produkts verknüpft wird. Das System identifiziert parasitäre Strukturen, Abschirmungslücken, Probleme im Rückstrompfad sowie Anfälligkeitsrisiken, die durch externe Felder und Massekonzepte entstehen.

Die elektromechanischen Prüfergebnisse stehen direkt in der 3D-Layout-Umgebung zur Verfügung, sodass Teams Gegenmaßnahmen verifizieren, Gehäusemerkmale anpassen und das Routing verfeinern können, ohne auf externe Solver oder aufwendige Modellvorbereitung angewiesen zu sein. Das Ergebnis ist eine klarere Sicht auf das EMV-Verhalten in frühen Designphasen, die fundiertere Entscheidungen während der Entwicklung ermöglicht.

Die Prüfungen auf parasitäre Antennen identifizieren Leiterführungen und Kupfergeometrien, die bei hohen Frequenzen unbeabsichtigt abstrahlen, und helfen so, Emissionsprobleme früh im Layoutprozess zu vermeiden.

Abschirmungsanalysen und Regelprüfungen bewerten Qualität und Kontinuität der Abschirmung im gesamten Design und helfen, Kopplungen, Emissionen und das Eindringen von Störsignalen zu verhindern.

Rückstrompfad-Prüfungen stellen sicher, dass Hochgeschwindigkeitssignale auf allen Lagen und über alle Boards hinweg einen durchgängigen, induktionsarmen Rückstrompfad nutzen.

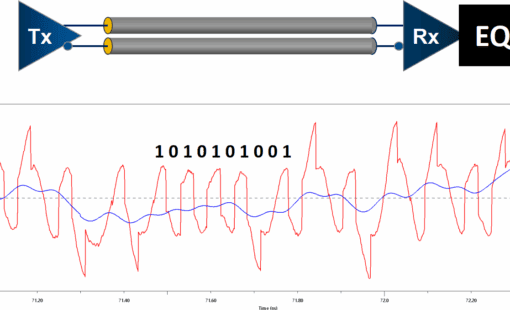

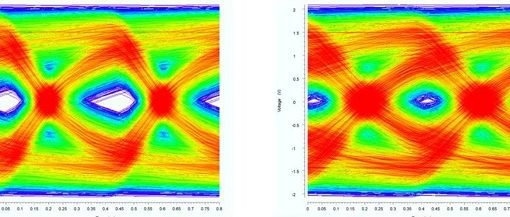

Signal-Integritätsprüfungen bewerten die physikalischen Bedingungen, die Impedanz, Reflexionen, Timing und die Qualität von Differenzpaaren in Hochgeschwindigkeitsnetzen beeinflussen.

Übersprechungsprüfungen identifizieren Routing- und PDN-Bedingungen, die unerwünschte Kopplung zwischen Signalen und Versorgungsnetzen in Single- und Multi-Board-Systemen verstärken.

Power-Integrity-Prüfungen stellen eine stabile Spannungsversorgung sicher, indem sie die Platzierung von Entkopplungskondensatoren, die PDN-Geometrie, Steckverbinder-Schnittstellen und stromführende Pfade bewerten.

EMC Adviser EX kann von folgenden Produkten gestartet werden

Design Force kombiniert konventionelles 2D-Design mit nativem 3D-Design und den neuesten Technologien in Benutzeroberfläche und Grafik für schnellstes Rendern und Aktualisieren.

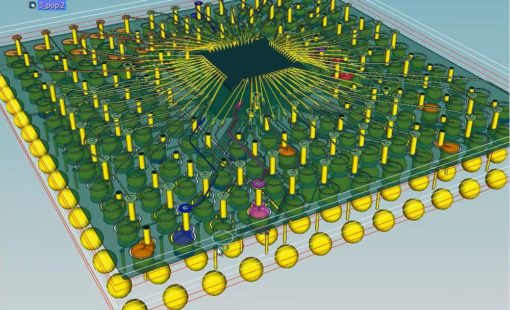

Zusätzlich zum Multi-Board PCB Design unterstützt Design Force auch die Entwicklung von IC Packages für Wire-Bond, Flip-Chip und High-Density Advanced Packaging

Relevante Blogbeiträge zum Thema

Lerne die beiden wichtigsten Grundlagen für den zuverlässigen Entwurf von High Speed Serial Links und erfahre, wie du Herausforderungen bei der Signalintegrität bei Geschwindigkeiten von mehreren Gbit/s meistern kannst.

EMV Probleme sind in der Leiterplatten-Konstruktionspraxis oft dafür verantwortlich, dass Re-Design-Zyklen notwendig werden. Aufgrund von immer kürzer Innovationszyklen von z.B. Mobiltelefonen oder IoT Applikationen wie Fitness-Trackern und vielen weiteren Elektronikprodukten sind diese zeitintensiven Re-Design-Zyklen unbedingt zu vermeiden.

Wussten Sie, dass der Ausdruck "Übersprechen" (engl. Crosstalk) aus der Zeit der Telefonzentralen stammt, in denen Mitarbeiter Anrufer miteinander verbunden haben, die manchmal ungewollt das Gespräch eines anderen hören konnten? Man sprach im wahrsten Sinne des Wortes über eine andere Leitung hinweg.

Dieser Vortrag ist keine Einführung in die DDR4-Technologie, sondern zeigt die Vorgehensweise bei der Implementierung von DDR4-Speicherschnittstellen mit Zuken CR-8000 von der Konzeptionsphase bis zur physischen Platzierung und Verlegung sowie der Validierung für SI und PI.

Am Beispiel der Analyse von SerDes Übertragungsstrecken wie PCI-Express, SATA oder USB3 erläutert unser Experte Ralf Brüning die Methodik einer Analyse- und Constraint-gesteuerten Baugruppenentwicklung mit CR-8000 Design Force.

Der Trend zu Anwendungen mit geringerem Stromverbrauch stellt Leiterplattendesigner vor neue Herausforderungen. Die engen Toleranzen für Timing und Spannung erfordern einen ganzheitlichen Entwurfsansatz, der High Speed Constraining und integrierte Analyseschritte zur Einhaltung der verschiedenen Entwurfsregeln verbindet.

In dieser Präsentation werden die Vor- und Nachteile der verschiedenen Simulationswerkzeuge sowie die Motivation für deren Einsatz im PCB-Entwurfsprozess vorgestellt.

Diese Webinar erläutert die Grundlagen von Signalintegrität und wie CR-8000 dabei hilft, die damit verbundenen Anforderungen zu beherrschen.

Im einem gemeinsamen Webinar mit Keysight Technologies betrachten wir die besonderen Anforderungen von DDR5 Speicherbausteinen und geben einen Überblick über den Design Prozesse mit CR-8000 von der Pre-Layout-Simulation über das dann zum constraint-basierten High-Speed-Routing bis zur Systemanalyse in Keysight ADS.