Zuken ermöglicht bessere Bauraumnutzung im PCB-Design durch echte 3D-Gehäusekonturen in CR-8000 Design Force

15. September 2015 – München und Westford, MA (USA) – Die neue Version 2015.1 der 3D-Multiboard PCB-Design-Umgebung CR-8000 von Zuken unterstützt Kollisionsprüfungen mit realistischen 3D-Gehäuseformen und ermöglicht dadurch eine weiter verbesserte Bauraumnutzung für hochkompakte Gehäuseformate, insbesondere im Bereich Consumer Elektronik. Darüber hinaus können in dem neuen Release Lagenaufbauinformationen direkt zwischen der 3D-Layoutapplikation CR-8000 Design Force und der Analyseumgebung Speedstack von Polar Instruments ausgetauscht werden. Dadurch kann der Lagenaufbau von Multi-Layer Designs optimiert werden.

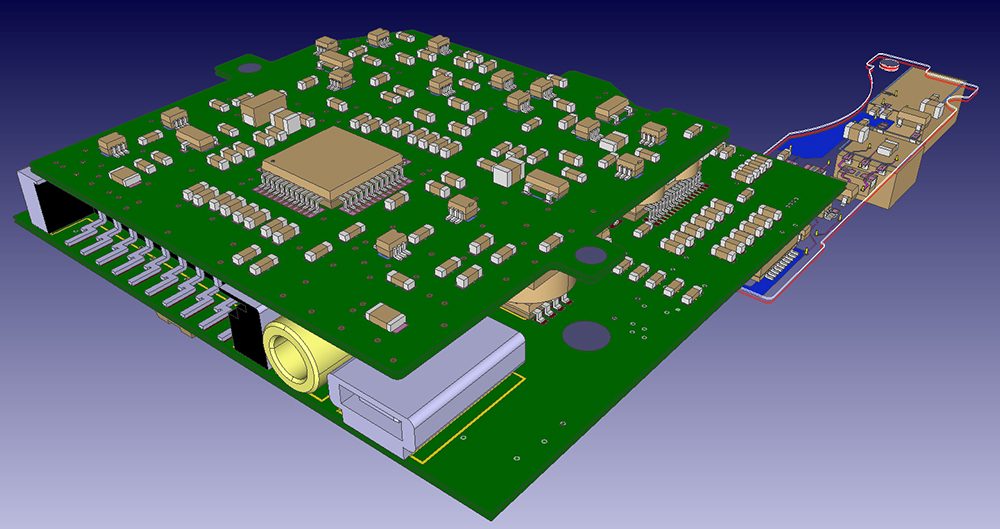

Die 3D Multi-Board PCB Design-Umgebung CR-8000 von Zuken ist die derzeit einzige produktzentrische PCB-Entwicklungsumgebung. Mit der Layout-Applikation CR-8000 Design Force können Designs jeder Komplexitätsstufe – vom kurzfristig verfügbaren Prototyp-Board bis zum komplexen Multi-Board Design in einer einzigen Umgebung durchgeführt werden.

CR-8000 hat sich hier als die technologisch führende Lösung erfolgreich etabliert. Die neue Version 2015.1 wird einen weiteren Beitrag zur Sicherung des Wettbewerbsvorsprungs unserer Kunden liefern.

Bob Potock, Vice President of Marketing bei Zuken USA

„Erfolgreiche Unternehmen beherrschen Entwicklungsrisiken durch die Anwendung eines strukturierten Produktentstehungsprozesses (PEP). Die rasche Zunahme elektronischer Funktionalität in modernen Produkten macht eine tiefere Verankerung der PCB-Entwicklung im Gesamt-Produktentstehungsprozess erforderlich. CR-8000 hat sich hier als die technologisch führende Lösung erfolgreich etabliert. Die neue Version 2015.1 wird einen weiteren Beitrag zur Sicherung des Wettbewerbsvorsprungs unserer Kunden liefern,“ kommentiert Bob Potock, Vice President of Marketing bei Zuken USA.

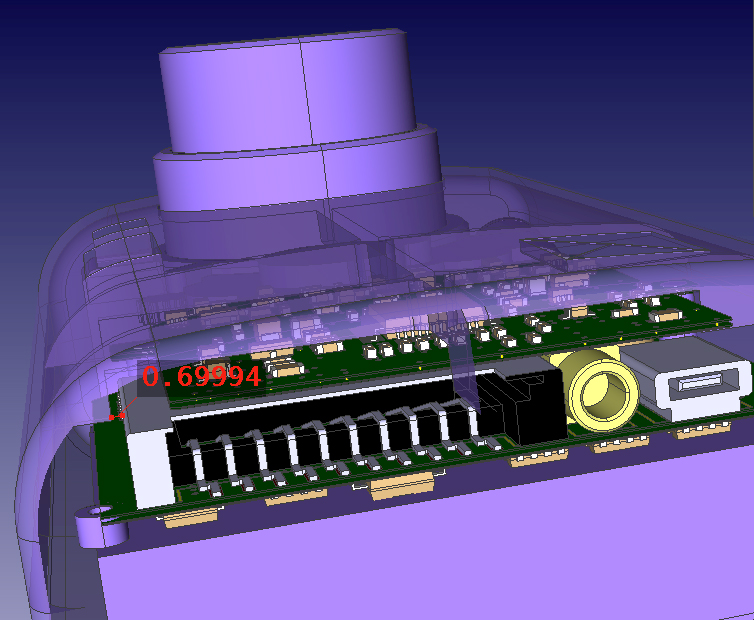

Abstandsanalyse mit realistischer 3D-Bauteildarstellung

Durch den Trend zur Verkleinerung von Produkten und Gehäusen wird es immer schwieriger, Board-Designs unter Berücksichtigung aller elektrischen und thermischen und mechanischen Aspekte im Gehäuse unterzubringen. Aus diesem Grund müssen heute bis zu 50% aller Designs in der Produktionsphase mit hohem Kostenaufwand nachgebessert werden.

Um solche Probleme besser in den Griff zu bekommen, können jetzt mit CR-8000 Design Force mithilfe von realistischen 3D-Komponentendarstellungen weit präzisere Abstands- und Kollisionsprüfung durchgeführt werden, als das mit den bislang üblichen, so genannten „Boundary Boxen“ möglich war. Die Fähigkeit, das Baugruppenlayout laufend mit dem Bauraum abzugleichen, ermöglicht eine engere Zusammenarbeit zwischen Elektronik- und Mechanik-Entwicklung und stellt dadurch einen wichtigen Beitrag zur Risikominimierung im Produktentstehungsprozess dar.

Optimierter Lagenaufbau

Lagenaufbau-Informationen können jetzt zwischen CR-8000 Design Force und der Analyseumgebung Speedstack von Polar Instruments ausgetauscht werden. Dadurch können die Anforderungen der Produktion bereits während des PCB-Layouts umfassend berücksichtigt werden. Über Speedstack stehen genaue und aktuelle Charakteristika der von Leiterplattenherstellern verwendeten Materialien zu Verfügung. Die zeitaufwändige und fehlergefährdete manuelle Übernahme von Lagenaufbau-Informationen entfällt dadurch.

Steigerung von Produktivität und Effizienz der Anwender

- Darüber hinaus wurden in CR-8000 2015.1 eine Reihe von weiteren Verbesserungen zur Steigerung der Anwenderproduktivität und –Effizienz realisiert. Dazu zählen:

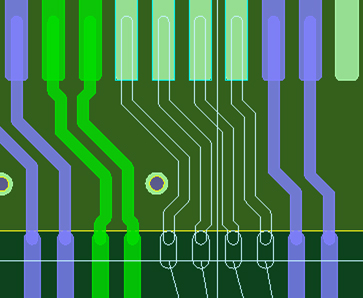

- Leiterbahnen können während der Bearbeitung unter Berücksichtigung von Produktionsertrag und Signalqualität optimiert werden.

- Automatische Anpassung der Leiterbahnbreite: Beim Routing mit den Funktionen Track/Route Differential Pair/Bundle Route wird die Leiterbahnbreite automatisch auf den für einen definierten Bereich festgelegten Wert geändert.

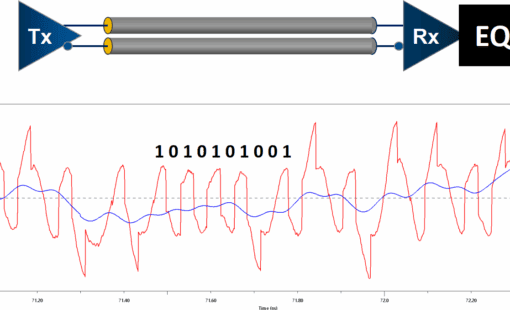

- Eine erweiterte Auswahl von Exportformaten im Waveform-Viewer vereinfacht die Dokumentation von Signalverläufen für Design Reviews.

Weitere Informationen finden Sie unter www.zuken.com/cr-8000