- Blog

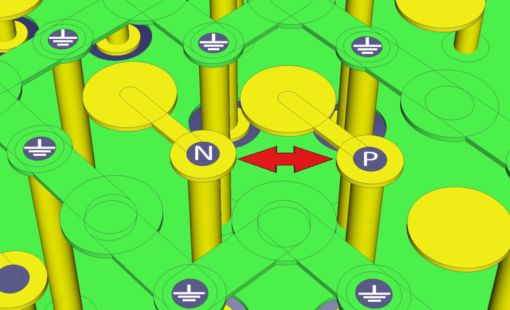

Zuken is taking its Simulation and Analysis Performance to the next level by introducing a new processing technology to its PI/EMI analysis tool. Multi-threading will speed up PI analysis which will give PCB designers a boost in productivity, especially when evaluating different design alternatives for PDN structures.

- Blog

EMV Probleme sind in der Leiterplatten-Konstruktionspraxis oft dafür verantwortlich, dass Re-Design-Zyklen notwendig werden. Aufgrund von immer kürzer Innovationszyklen von z.B. Mobiltelefonen oder IoT Applikationen wie Fitness-Trackern und vielen weiteren Elektronikprodukten sind diese zeitintensiven Re-Design-Zyklen unbedingt zu vermeiden.

- Blog

Was tun, wenn Ihr nächstes Projekt besonders hohe EMV-Anforderungen stellt und schneller als jemals zuvor abgeschlossen werden muss?

- Blog

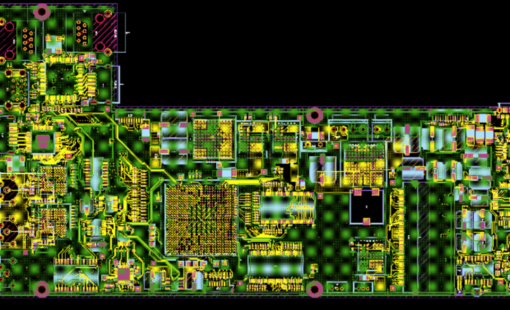

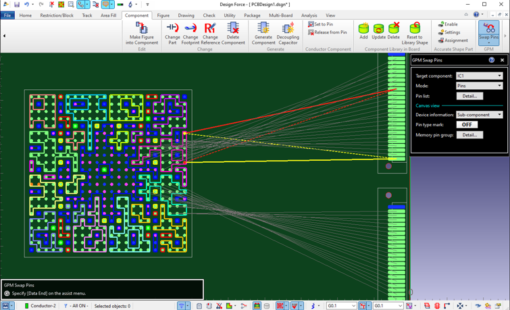

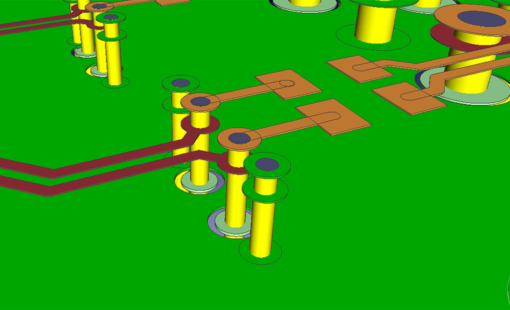

CR-8000 2020 is Zuken’s flagship PCB design platform, and I’m pleased to share some of the most exciting details of the new product release with you. But before we get into the new product release discussion, you may be wondering why we call it a platform and not a tool. CR-8000 2020 has all the bells and whistles for electronic subsystem development.

- Blog

In part 1 of this blog we took a back-to-basics approach and discussed line impedance and its effects in signal integrity. As every electrical conductor comprises capacitance, an inductance, and a frequency-dependent ohmic resistance, and with increasing frequencies, these electrical characteristics will influence and distort the signal.

- Blog

Impedance and impedance control belong to the oldest and most often discussed topics in PCB design. They are especially important with the high-speed design when related to signal integrity. In this, the first of a two-part blog, we’ll go back to the basics of impedance/impedance control and consider what influences line impedance. In part two, we’ll set about controlling it.

- Blog

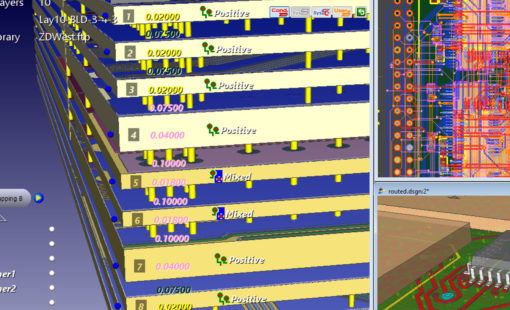

We’re happy to announce that Speedstack, Polar Instruments’ layer stackup design/documentation tools, can now be directly linked to Zuken’s CR-8000 Design Force and DFM Center.

- Blog

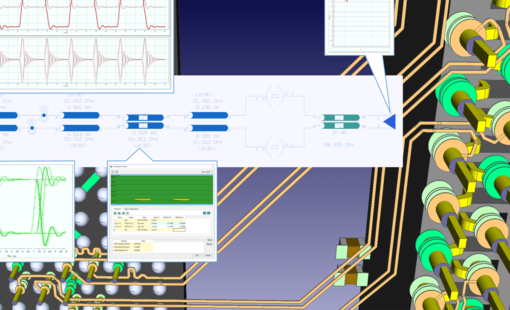

CR-8000 Design Force can help you verify your design before you send it out to manufacture. Before running any signal integrity analysis in Design Force, you must assign device models to the pins in your components using the Constraint Browser.

- Blog

I don’t think I’m generalizing when I say that designers working on complex high speed designs really don’t want to expend a lot of time and effort dealing with power integrity problems. And they especially don’t want to do it using tools that are detached from their design flow. In today’s complex PCBs, we’re talking advanced processors, complex FPGAs and superfast memories, which all share various voltage ranges.

- Blog

In the final installment of this blog series, you can learn how to use build-up layers and premium FPGAs to deal with the signal integrity challenges arising from high-speed signals in a 3D design capture world.

- Blog

This is the second in my series of blog posts looking at the challenge of maintaining PCB signal integrity with now-common ultra-high speeds and growing adoption of PCB design environments to design in true 3-D. Today I focus on vias and the use of return vias to overcome the issues highlighted in Part 1.

- Blog

Ultra-high signal speeds demand detailed consideration of the third dimension in PCB design, including via structures and layer stacks. Today I’m going to focus on the challenge. In my two subsequent posts I’ll be reviewing what PCB designers can do to meet that challenge.

- Blog

I’d like to explain to you in straightforward terms what S-Parameters are and why they’re so useful. When I say “straightforward”, I mean that in a technical sense, but this is a specialised area. If you’re not designing high-speed PCBs, or you don’t know much about signal integrity, you might want to tune out now.