Do you know what a »Yogi-ism« is? Well, I didn’t, because I’m not an American, to begin with, and consequently I have no clue of baseball. But Wikipedia and a number of similar sites were quick to help: Yogi-ism goes back to the name of the late Yogi Berra (1925 – 2015), an American professional baseball catcher, who was an 18-time All-Star and won 10 World Series championships – more than any other player in MLB history. After his career as a player, he turned to coaching, where he became famous for his “impromptu pithy comments, malapropisms, and seemingly unintentional witticisms, known as Yogi-isms” (source: Wikipedia).

So, what does that mean? Well, he created a wealth of seemingly nonsensical phrases – which often had “an underlying and powerful message that offered not just humor, but wisdom”. Want an example? “Ninety percent of baseball is mental; the other half is physical”. Or about his favorite restaurant in St. Louis and why he no longer went there: “Nobody goes there anymore. It’s too crowded.” And finally: “It ain’t over, till it’s over.”

The future of Chip Scale Integration

How did I get to look up Yoga Berra and his Yogi-isms? Well, I came across it in a presentation on the future of computing and chip scaling, by Prof. Subramanian S. Iyer, Distinguished Professor at the UCLA Electrical and Computer Engineering, that my valued colleague, Humair Mandavia, from the Zuken Sozo Center in San Jose sent me with a request to write up a press release on Zuken’s support of the UCLA’s CHIPS program.

UCLA CHIPS consortium consists of industrial partners from material suppliers, equipment manufacturers, foundries to system integrators, and includes support from universities and government agencies and industrial consortia, working collaboratively to develop new packaging technologies and system architectures and develop the next generation workforce.

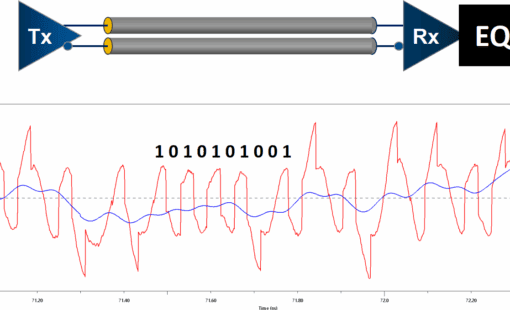

In this presentation, after reviewing the evolution of computing power and chip scaling, Prof. Iyer comes to the conclusion that the industry is facing a chasm between the soaring demand for computing power that, among others, calls for heterogeneous functional integration, and the slowing progress of chip-scale integration (“Moore’s law”) because of soaring cost and miniaturization challenges.

If you can’t scale the chip, you should scale something else

And here is where Yogi Berra comes into the story: After concluding that functional integration and chip-scaling are in a deadlock, Prof. Iyer comes up with a slide that asks the famous question: “What would Yogi say!” and he provides the answer: “So, if you can’t scale the chip, you should try to scale something else!”

What that “something else” is, and what Zuken contributes to it, can be read in Zuken’s latest press release »Zuken partners with UCLA Department of Engineering to develop cost-effective IC manufacturing methodologies for heterogeneous computing«.

Related Content

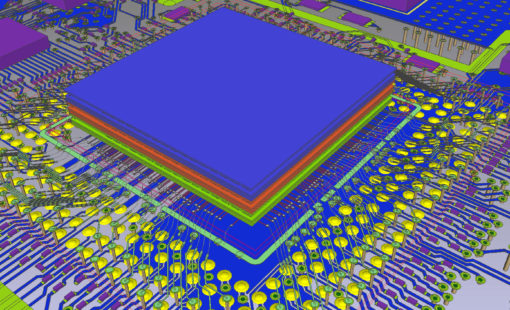

- Products

Zusätzlich zu den hochentwickelten Funktionen für das PCB-Layout bietet Design Force die Möglichkeit des Co-Designs von Chips, Gehäusen und Leiterplatten, so dass ein hierarchisches 3D-Design in Echtzeit ermöglicht wird.

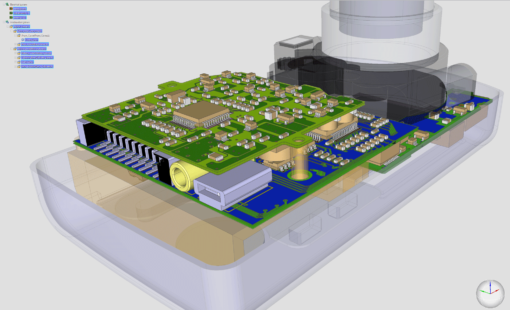

- Products

Design Force kombiniert konventionelles 2D-Design mit nativem 3D-Design und den neuesten Technologien in Benutzeroberfläche und Grafik für schnellstes Rendern und Aktualisieren.

- Products

CR-8000 umfasst eine Suite von Anwendungen, die den gesamten Lebenszyklus des PCB Engineerings abdecken.