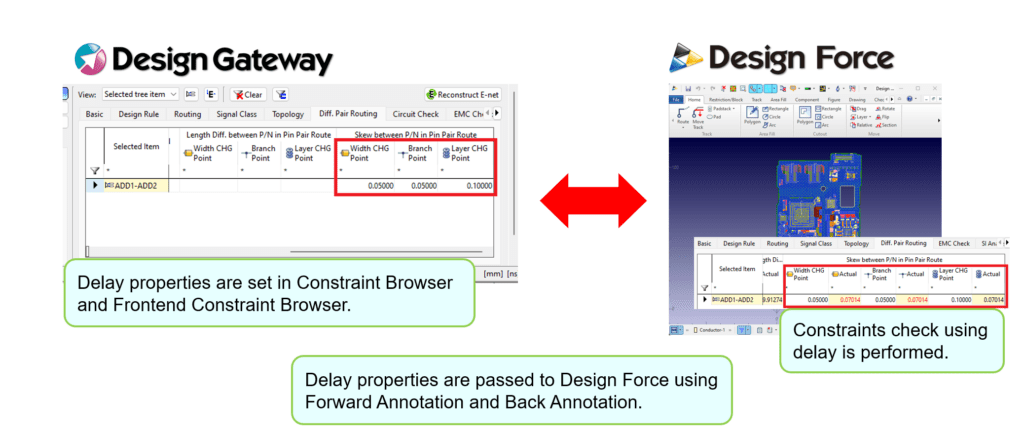

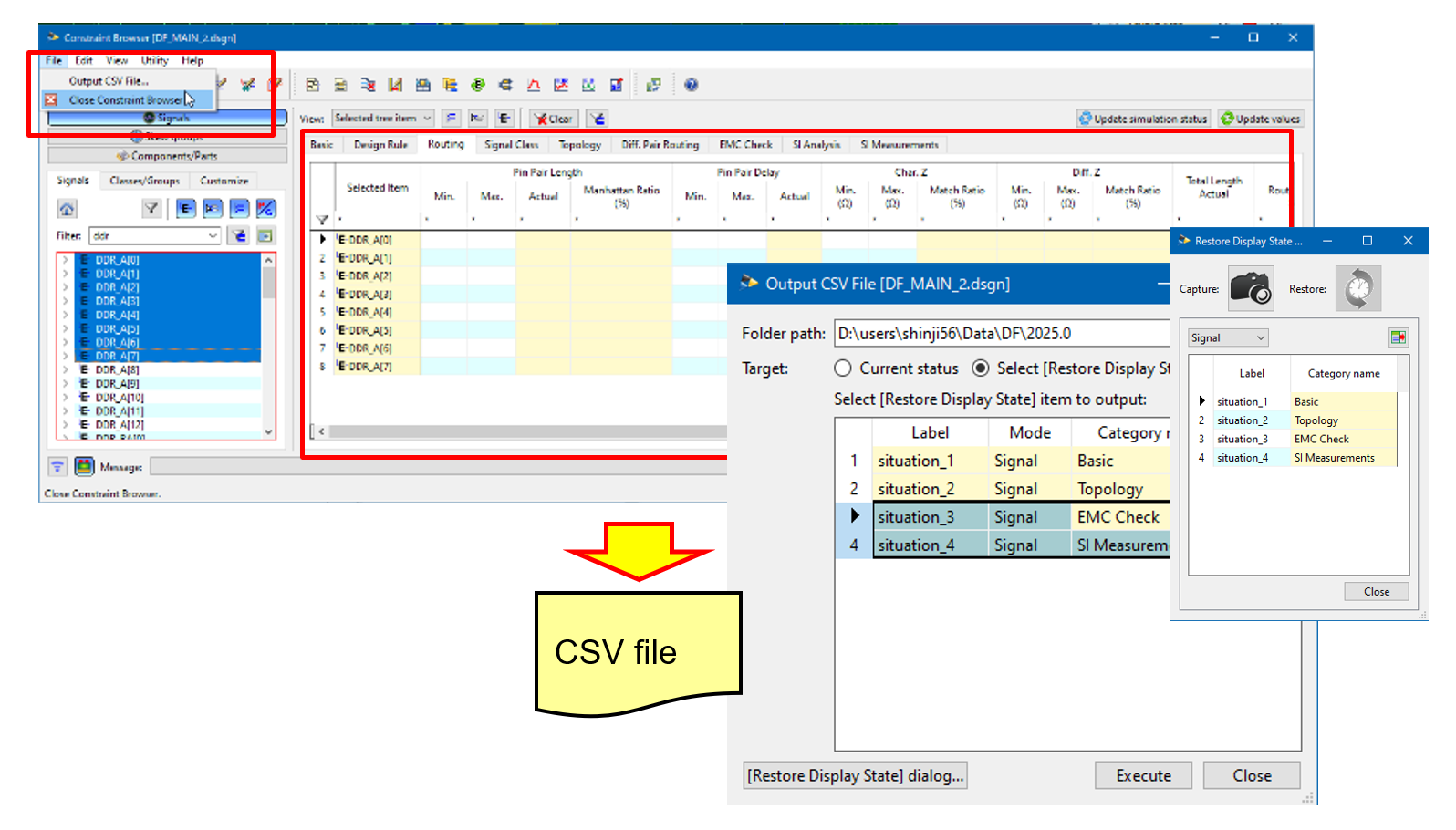

Advanced Constraint Propagation

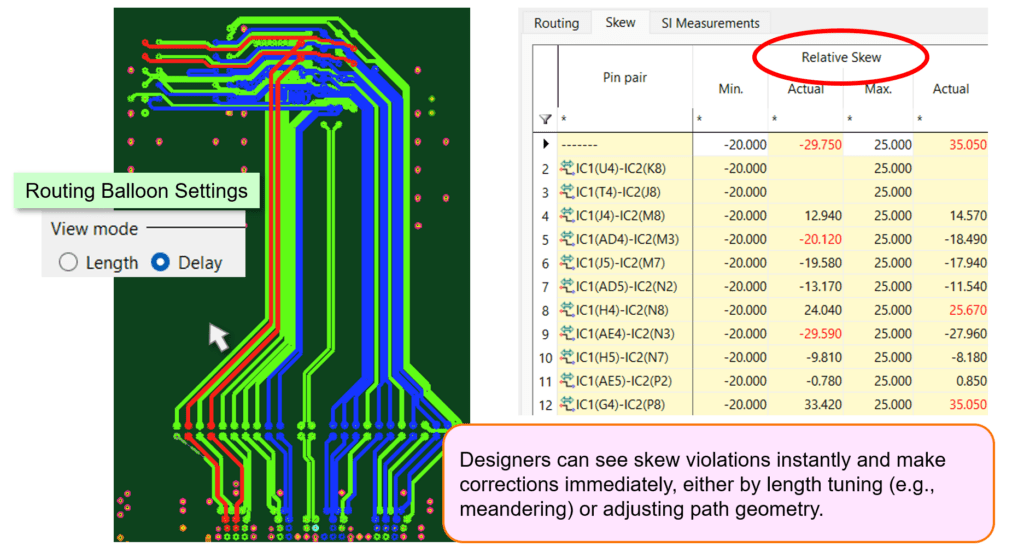

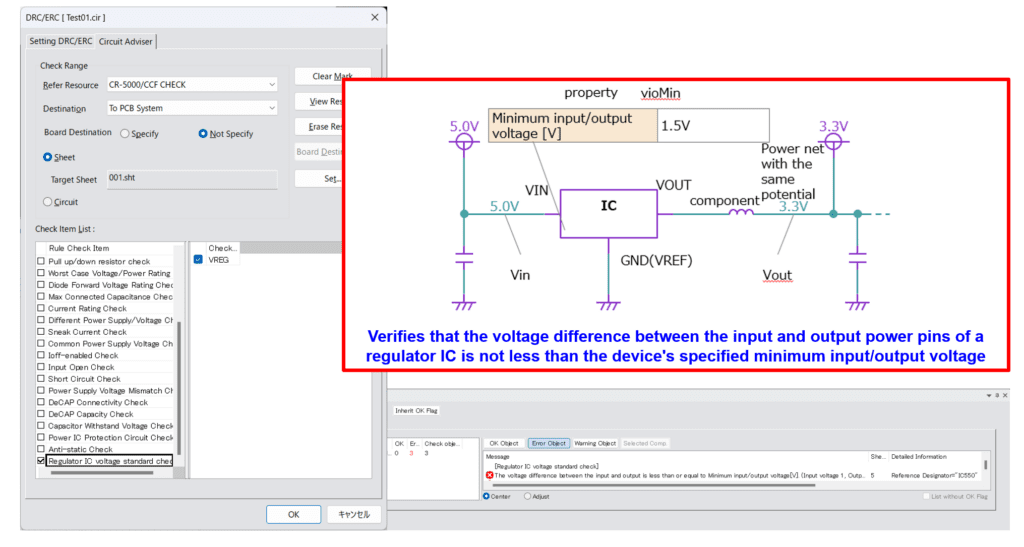

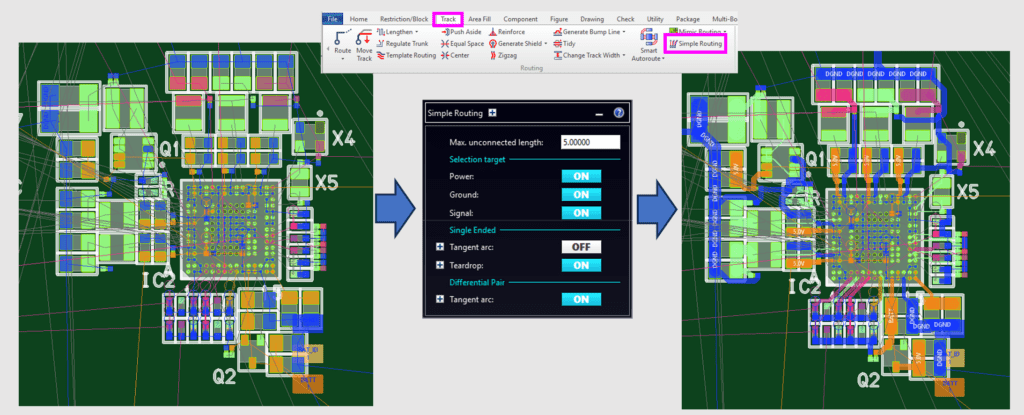

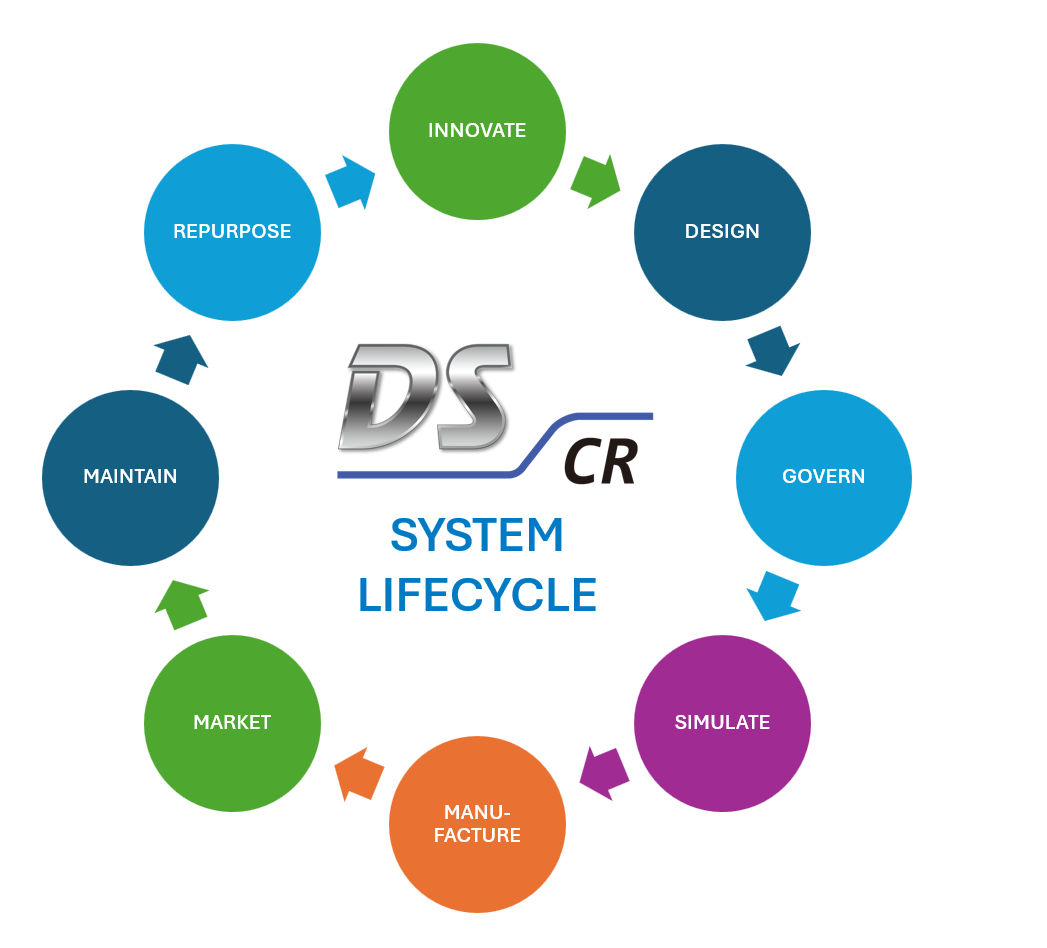

Release 2025 improves the transfer of timing, skew, and delay constraints between Design Gateway (schematics) and Design Force (physical layout), offering the following benefits:

- Seamless implementation of specifications from system planning to physical layout

- Consistent application of constraints for delays, skew, and topologies in high-speed interfaces (e.g., DDR, PCIe, SerDes)

- Reduced need for manual alignment, lowering the risk of inconsistent constraint definitions