Eine sorgfältige Planung der Signalübertragung wird bei zukünftigen Ultra-High-Speed-Systemen aufgrund der fortschreitenden Entwicklung bei der IC-Buffer-Technologie und der daraus resultierenden vielfältigen Design-Constraints immer komplexer. Moderne Signalübertragungsstandards wie die schnellen differenziellen SERDES-Links und die dort implementierten Protokolle (USB, SATA, PCIe usw.) bereiten PCB-Designern zunehmend Kopfzerbrechen. Zusätzlich kann das verlustbehaftete Verhalten des Leiterbahnmaterials (i.d.R. Kupfer) die Signalübertragungsleistung bei höheren Datenraten zusätzlich beeinträchtigen.

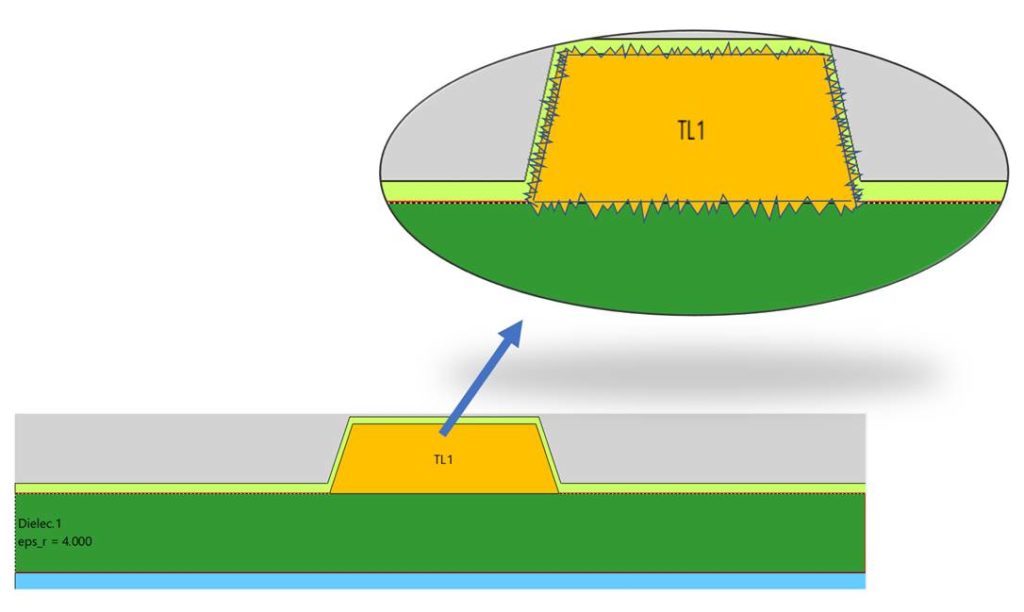

Ein genauerer Blick wie die Oberfläche von PCB-Leiterbahnen quasi unter dem Mikroskop ausschaut, offenbart ein potentielles Problem. In der Welt der Leiterplattenhersteller existiert so etwas wie eine vollkommen glatte Kupferoberfläche bei den zur PCB-Herstellung verwendeten Kupferfolien gar nicht. Kupfer weist immer ein gewisses Maß an Materialrauheit (Surface Roughness) auf, diese ist ja sogar notwendig, um die Haftung des Kupfers auf dem Dielektrikum während des Verpressens der einzelnen Lagen einer Leiterplatte zu verbessern. Aber insbesondere bei digitalen High-Speed-Designs kann dieser Oberflächenrauhigkeitseffekt (Conductor Surface Roughness Effect) des leitenden Materials den Stromfluss über die Geometrie der Leiterbahnen erheblich beeinflussen.

Bei Gleichstrom und auch bei niederfrequentem Wechselstrom spielt es eigentlich keine Rolle, wie rau das Kupferoberflächenprofil einer Leiterbahn ist. Aber bei modernen High-Speed-Anwendungen im GHz-Bereich (in Bezug auf Datenübertragungsraten) ist die effektive Durchdringungstiefe in den Leitern relativ gering (der sogenannte Skin Effekt), womit dann der größte Teil des Stromflusses an der Oberfläche des Leiters stattfindet. Hier wirkt sich dann aber die Oberflächenrauheit direkt auf den Stromfluss aus (höherer Widerstand) und verursacht höhere Verluste als normalerweise üblich. Man kann diese Situation mit einem Rennwagen vergleichen, der auf unbefestigten Wegen bei weitem nicht so schnell fahren kann wie auf einer ebenen Rennstrecke.

Um diesem Effekt entgegenzuwirken, bieten die meisten Kupferfolienhersteller speziell gefertigte “glatte” Kupferbleche, sogenannte Elektrodepositionsfolien (ED-Folien), an, die auf Wunsch bei der Leiterplattenherstellung mit unterschiedlichen Rauheitsgraden verwendet werden können. Dies wirkt sich allerdings direkt auf die Produktionskosten aus. Die Kenntnis über alle Gestaltungsspielräume bei der Signalübertragung kann daher ein Schlüsselfaktor sein für den Erfolg eines Designprojektes. Und die Oberflächenrauheit schränkt diesen Spielraum mit Sicherheit ein.

Simulation im Hinblick auf Leitungsverluste, Signaldämpfung und Skin-Effekt, Modellierungsfragen

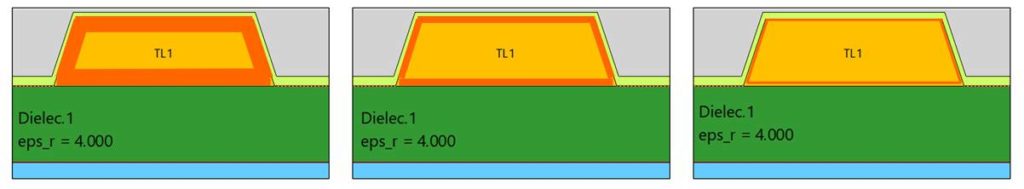

Seit vielen Jahren werden PCB-Leitungen in Signal-Integrity-Analysen als verlustbehaftete Elemente behandelt. Diese “Verluste” ergeben sich aus verschiedenen individuellen Effekten, wie die Leitungsverluste, der dielektrischer Verlust und in geringerem Maße auch Strahlungsverluste. Alle diese verschiedenen Verlustgrößen sind frequenz-, material- und auch geometrieabhängig. Bei hohen Frequenzen (z. B. jenseits von 1 GHz) wirkt sich dann die Oberflächenrauheit des Kupfermaterials ganz erheblich auf den Gesamtverlust aus. Der “Skin-Effekt” beschreibt dabei die Tendenz des Stroms, sich mit zunehmender Frequenz an der äußeren Oberfläche des Leiters zu konzentrieren. Der Bereich des Kupfers in dem dann Strom fließt wird als Eindringtiefe δ (eng. Skin Depth). Dies wird in der nachfolgenden Abbildung veranschaulicht, in der die orangefarbenen Bereiche die unterschiedliche Skin-Tiefe auf einem Kupferleiterquerschnitt darstellen.

Die Skin-Tiefe ist der Bereich zwischen der äußeren Oberfläche und dem Punkt, an dem die Stromdichte auf etwa 37 % ihres Wertes an der Oberfläche abfällt. Für die Berechnung der Skin-Tiefe werden die Frequenz des Wechselstromsignals, der spezifische Widerstand des leitenden Materials und dessen relative Permeabilität benötigt. Sie lässt sich mit der folgenden Formel (1) herleiten:

δ=1/ √(πfµs) (1)

In diesem Fall ist die Skin-Tiefe (in m) durch die betrachtete Frequenz f (in Hz) definiert, µ gibt die Permeabilität des Materials an (µo, oder 1,2566E-6 H/m für die meisten Materialien), s ist die Leitfähigkeit des Materials (in Siemens/m oder 1/r, wobei r der spezifische Widerstand in Ohm/m ist). Vereinfacht (für den Fall von reinem Kupfer) kann dies auf die nachstehende Formel (2) reduziert werden, die für eine erste Abschätzung von δ gut geeignet ist (aus [9]):

δ=66* √(1/f) (2)

Nur um Ihnen diesen Faktor in seinen Extremwerten zu verdeutlichen: Bei 50 Hz beträgt die Skin-Tiefe in Kupfer etwa 9,3 mm. Bei höheren Frequenzen wird die Skin-Tiefe sehr viel kleiner, bis hinunter zu 2µm bei 1GHz (diese Frequenz haben wir in den meisten heutigen Kommunikationsverbindungen), bei einer Frequenz von 50GHz kann die Skin-Tiefe dann winzige Werte von unter 300nm betragen (in dem Fall 0,295µm).

Die Auswirkungen des Skin-Effekts auf den Entwurf von High-Speed-Design Baugruppen

Wenn der Bereich, in dem sich Stromflüsse konzentrieren, eher rau als glatt ist, vergrößert sich damit die effektive Leiterlänge, da der Strom dazu neigt, den Konturen zu folgen (dabei sollte erwähnt werden das sich das reale elektromagnetische Verhalten deutlicher komplexer darstellt, Details dazu sind in [3] hervorragend beschrieben).

Bei den hohen Frequenzen und den Datenraten heutiger SERDES-Verbindungen wie z.B. PCI-Express, USB3, HDMI usw. erhöht sich der resultierende effektive Widerstand durch die Leitungs- und durch die di-elektrische Verluste, dies beeinträchtigt die Signalübertragungsqualität und die Bitfehlerrate (BER) zu einem gewissen Grad. Das vom Simulator intern verwendete Leitungs- beruht auf kaskadierten RLCG-Elementen (jeweils einheitslos als Leitungsparameter) deren jeweilige Werte mithilfe des internen numerischen Field-Solvers bestimmt werden. Die frequenz- und materialabhängigen Verluste (die sich konkret jeweils auf die Parameter R’ und G’ auswirken) beeinflussen dann die Signallaufzeit durch eine erhöhte Dämpfung.

Berücksichtigung von Oberflächenrauheit und Verlusten in der Simulation

Mit der fortschreitenden Verwendung von Signal-Integrity-Analysen wurden im Laufe der Jahre verschiedene Modellierungsansätze entwickelt, um einen Korrekturfaktor für die Kupferoberflächenrauheit zu bestimmen. Eine der populärsten Methoden ist das Hammerstad-Jensen-Modell [6], bei dem der theoretische Ansatz auf die Arbeiten von Samuel Morgan [1] zurückgeht, der dieses Konzept 1949 durch die Einführung eines mathematischen “Korrekturwertes” für die Rauheit definierte. Dieser “Morgan-Korrelationsfaktor” Kr für die Oberflächenrauheit eines Leiters beschreibt die relative Rauheit der Oberfläche als das Verhältnis einer glatten Oberfläche zu einer rauen Oberfläche. Laut den Untersuchungen von Industrieexperten [2] korreliert dieses Modell in der Praxis für Microstrip-Geometrien bis zu mehreren GHz und für eine Oberflächenrauheit von weniger als 2 𝜇m ausreichend gut. Es sollte jedoch erwähnt werden, dass in den letzten Jahren andere Modelle (wie das Huray-Modell, siehe dazu [6]) für die Modellierung von Verbindungen mit hohen Datenraten diskutiert werden.

Die Berücksichtigung der Oberflächenrauheit in der CR-8000 Signal-Integrity-Analyse

Die meisten Entwickler erwarten vermutlich nicht, dass sie sich während Ihres Designprojekts mit der Rauheit von Kupfer befassen müssen – sie gehen davon aus, dass dies nur die Kollegen betrifft, die die Technologie, also die Eckpunkte des Leiterplattenaufbaus, der verwendeten Materialien und die Details des Fertigungsprozesses festlegen. Sehr wahrscheinlich ist diese Annahme in den meisten Fällen auch korrekt. Aber eine andere oft verbreitete Annahme stimmt dabei aber nicht: Dass eine solche Analyse den Einsatz von hochentwickelten 3D-EM-Simulationswerkzeugen erfordert.

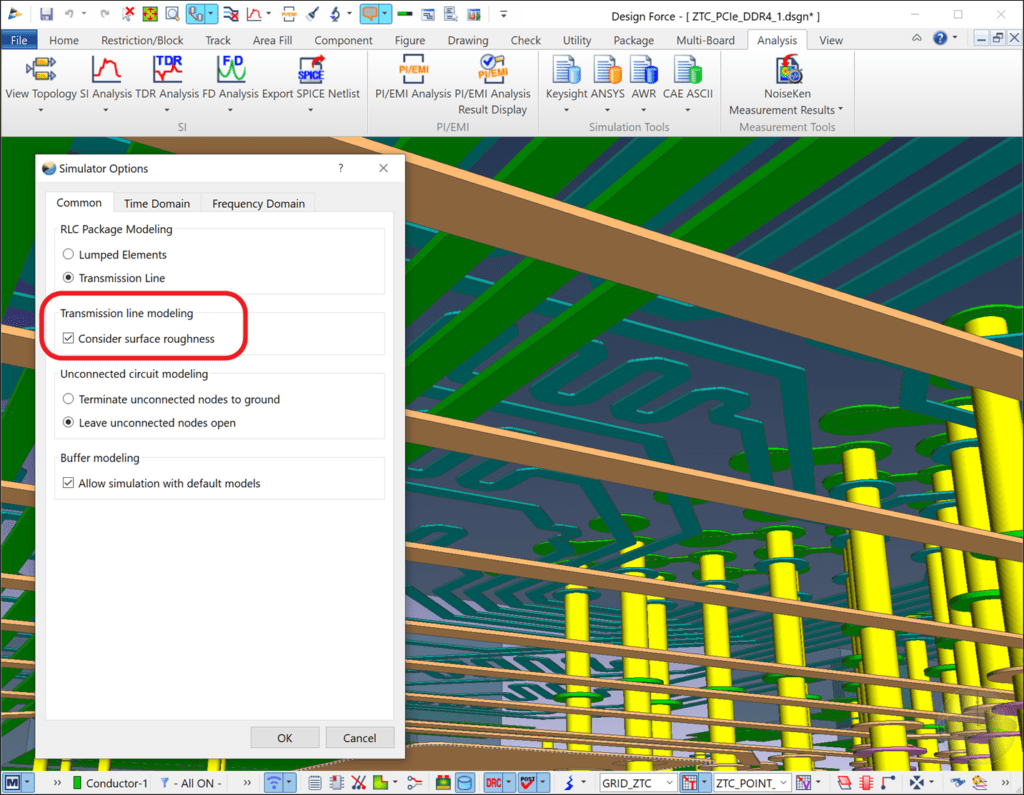

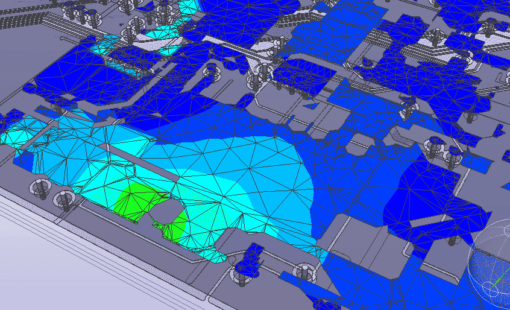

Korrekterweise muss gesagt werden, dass 3D-EM-Tools eine Möglichkeit sind, solche Fragen anzugehen, und solche Simulationswerkzeuge sind in der Tat sehr mächtig, um alle verschiedenen Aspekte wie detaillierter Stromflusses, der verschiedenen Verluste, der Oberflächenrauheit und der Skin-Tiefe zu untersuchen. Weniger bekannt ist allerdings, dass die integrierten Signal-Integrity-Simulationswerkzeuge in CR-8000 ebenfalls den Hammerstad-Jensen-Ansatz implementiert haben, so dass der Anwender eine Korrektur im Hinblick auf die Kupfer-Rauheit für eine Signalintegritätsanalyse (sowohl im Zeit- wie auch im und Frequenzbereich) aktivieren kann. Wie in Abbildung 4 dargestellt, wird dies im Dialogfeld bei den Simulator-Optionen aktiviert. Es sind keine komplizierten Einstellungen erforderlich, zusätzlich sei erwähnt das der Simulationsprozess keinerlei Leistungseinbußen erfährt.

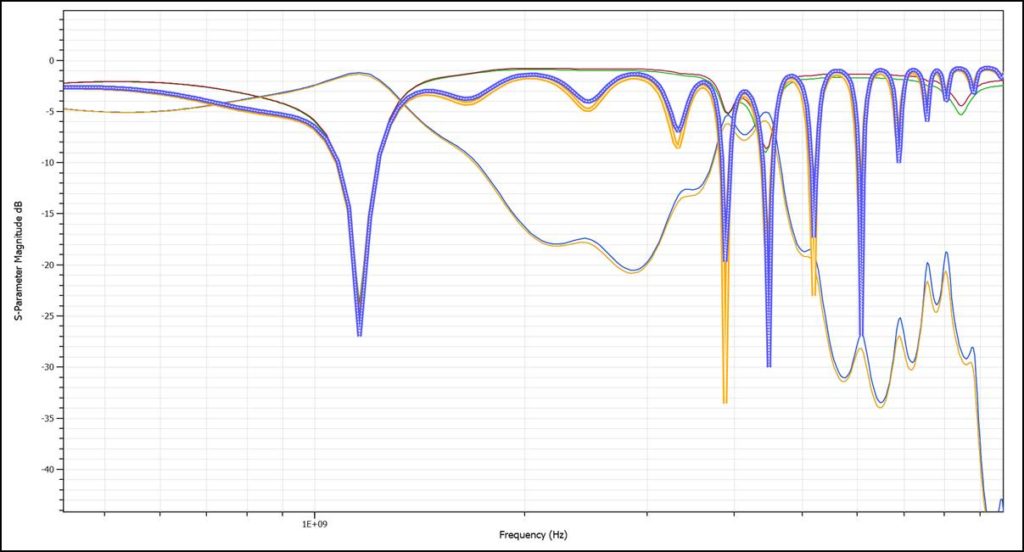

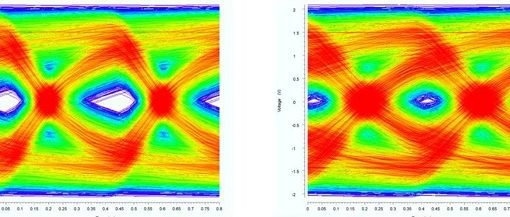

Die Auswirkungen werden allerdings erst bei höheren Frequenzen bzw. bei hoher Datenrate in der Zeitbereichssimulation und auch in der Frequenzbereichsanalyse sichtbar. Die Untersuchung der simulierten S-Parameter zeigt in solchen Fällen direkt den zunehmenden Einfluss mit steigender Frequenz. In Abbildung 5 ist das Ergebnis einer FD-Simulation eines DDR4-Signals mit und ohne eingestellte Option dargestellt. Bei höheren Frequenzen (die Abbildung zeigt den Bereich zwischen 500 MHz und 10 GHz) zeigen die relevanten Parameter (z.B. Insertion Loss) einen gewissen Unterschied. Dieser Unterscheid erscheint zwar gering, er kann sich aber dennoch erheblich auf die Augenöffnung und die Kalkulation der Bitfehlerrate in SERDES-Simulationen auswirken.

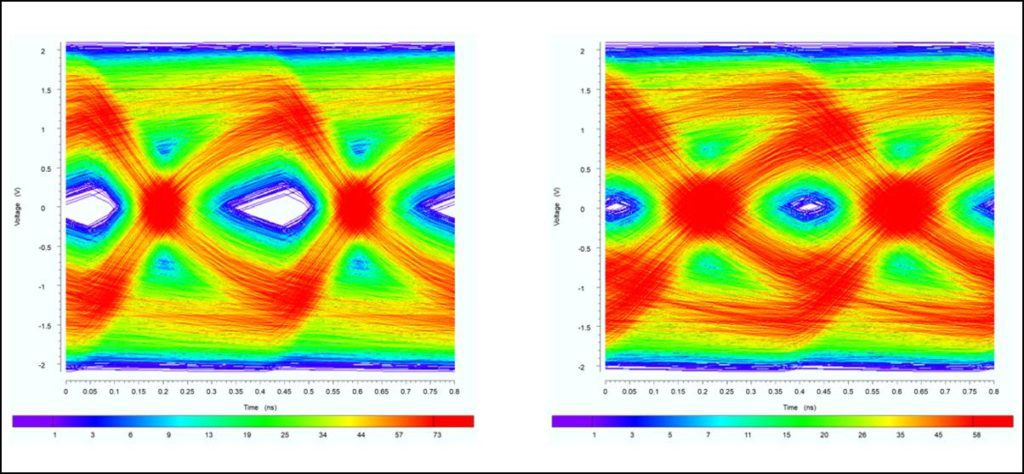

In Abbildung 5 sind die Ergebnisse einer solchen SERDES-Simulation (bei einer Datenrate von 8 GB/s) mit und ohne aktivierter Oberflächenrauheit dargestellt, die eine deutlich unterschiedliche Charakteristik aufweisen.

Zusammenfassung

Beim Leiterplattenaufbau gibt es keine perfekt glatten Oberflächen der leitenden Strukturen. Ich selber war nie ein Verfechter einer Impedanz-Definition bis auf zwei Nachkommastellen, soll heißen, einer Regeldefinition bis in mikroskopische Details hinein. Aber in diesem Punkt müssen Leiterplattenentwickler sich darüber im Klaren sein, dass sich der Skin-Effekt deutlich auf den AC-Widerstand von High-Speed-Signalen (!) auswirkt und daher die Signalformen jenseits bestimmter Frequenzen signifikant beeinträchtigt werden – mit der Möglichkeit, das jeweilige Augendiagramm zu schließen. Heutzutage haben sich daher die Methoden zur Simulation der Oberflächenrauheit weitgehend durchgesetzt. Eine dieser Methoden ist in den CR-8000 Signal Integrity Simulationswerkzeugen implementiert und ermöglicht eine sehr einfache Benutzung.

Grade in Zeiten, in denen die Datenraten vieler Anwendungen in den Multi-GHz Bereich vorstoßen, ist die Kenntnis dieser grundlegenden Konzepte des Verhaltens von Übertragungsstrecken von entscheidender Bedeutung. Mit CR-8000 können Sie alle relevanten Analyseschritte als integralen Bestandteil des PCB-Entwurfsprozesses durchführen, ohne dass Sie komplizierte 3D-Simulations-Tools für solche Aufgaben benötigen.

Zum Schluss möchte ich den großen Eric Bogatin zitieren, nur für den Fall, dass Sie sich gerade fragen, ob Sie sich nun um die Oberflächenrauheit des Leiters und deren Einfluss auf den Skin-Effekt kümmern sollten: “Es kommt darauf an…” (im Original: “it depends”). Aber sicher ist, dass Sie in CR-8000 jeweils nur einen Mausklick benötigen, um die integrierten Signal-Integrity-Analyse zu erhalten die Ihnen dabei helfen können, potentiellen Ausschuss in der Leiterplattenfertigung zu vermeiden.

Quellen:

1) Samuel P. Morgan, “Effect of surface roughness on eddy current losses at microwave frequencies,” Journal of Applied Physics, vol. 20, no. 4, pp. 352–362, Apr 1949.

2) Bert Simonovich: “Practical Method for Modelling Conductor Surface Roughness Using Close Packing of Equal Spheres”, 3) DesignCon 2015

3) Eric Bogatin, Yuriy Shlepnev, Chun-Ting “Tim” Wang Lee: “Back to basics: the onset of skin effect in circuit board traces”, DesignCon 2017

4) Yuriy Shlepnev, Chudy Nwachukwu: “Practical methodology for analysing the effect of conductor roughness on signal losses and dispersion in interconnects”, DesignCon 2012

5) Hinaga, Koledintseva, Anmula, Drewniak: “Effect of Conductor Surface Roughness upon Measured Loss and Extracted Values of PCB Laminate Material Dissipation Factor”, IPC 2009

6) Erick Bracken; “A Causal Huray Model for Surface Roughness”, DesignCon 2012

7) E. Hammerstad and O. Jensen, “Accurate Models for Microstrip Computer-Aided Design,” in IEEE MTT-S Intl. Microwave Symposium Digest, Washington, DC, 1980.

8) Eric Bogatin et al.: “Which one is better? Comparing Options to Describe Frequency Dependent Losses”, DesignCon 2013

9) Ness Engineering: Skin Depth Calculator

10) Wikipedia: Skin Effect

This post was first published on ecadstar.com

- Webinare

Am Beispiel der Analyse von SerDes Übertragungsstrecken wie PCI-Express, SATA oder USB3 erläutert unser Experte Ralf Brüning die Methodik einer Analyse- und Constraint-gesteuerten Baugruppenentwicklung mit CR-8000 Design Force.

- Webinare

Diese Webinar erläutert die Grundlagen von Signalintegrität und wie CR-8000 dabei hilft, die damit verbundenen Anforderungen zu beherrschen.