Digitale High-Speed Bausteine werden heute mehr oder weniger überall in elektronischen Anwendungen (IT, Automotive, Industrieelektronik, IoT) eingesetzt. Dabei liegen die Schaltzeiten im Bereich von deutlich unter 1ns bis hin zu 100 ps.

Daher werden Bedeutung und Mechanismen von Leiterbahnimpedanz/Wellenwiderstand (typischerweise als „charakteristische Impedanz“ bezeichnet) und auch ihre Auswirkungen auf die Signalintegrität intensiv diskutiert. Im Allgemeinen scheinen diese Aspekte von Leiterplattendesignern inzwischen gut verstanden zu werden.

Einfach ausgedrückt beschreibt eine „Impedanz“ ein Maß für den Widerstand, den eine Schaltung einem Strom entgegensetzt, sobald eine Spannung angelegt wird. Bei digitalen Übertragungsleitungen ist Impedanzkontrolle ein seit mehr als 20 Jahren etabliertes Konzept. Seit einigen Jahren wird der Begriff Impedanz aber auch verwendet, um das Verhalten von Stromversorgungsystemen von Leiterplatten (sog. Power Delivery Networks – PDN) zu beschreiben. Genau diese PDN-Impedanz bereitet PCB Designern zunehmend Kopfzerbrechen, da IC-Hersteller inzwischen sehr enge „Zielimpedanzgrenzen“ definieren, die ein Design erfüllen muss. Werte von wenige Milliohm sind hier meist die Regel.

Sie sind sich als Layouter oder Hardware-Entwickler nicht sicher, was der Begriff PDN-Impedanz für Sie konkret bedeutet und worauf Sie achten müssen? Dann lassen Sie uns einen genaueren Blick auf PDN-Impedanz und PDN-Zielimpedanz werfen und lassen Sie mich versuchen, ihre Relevanz für das Design moderner High-Speed Boards zu erklären.

Impedanz und ihre Abhängigkeit zu Kapazität und Induktivität

Die theoretischen Grundlagen spielen bei der Beantwortung von Fragenstellungen rund um die Impedanz eine elementare Rolle, hier seien nur das Ohm’sche Gesetz, die Kirchhoff‘schen Gesetze und für die Induktivität die Faraday’schen Gesetze genannt.

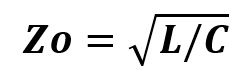

Aber auch ohne allzu tief in die Theorie einzutauchen ist den meisten Leiterplattendesignern bewusst, dass für Leiterbahnen der sogenannte Wellenwiderstand „Z0“ in direktem Zusammenhang (der Einfachheit halber verlustfrei) mit der Leiterbahninduktivität (L) und der Leiterbahnkapazität (C) steht. Oder als Formel:

Die Leitungskapazität hängt dabei direkt von der Geometrie innerhalb des Leiterplattenaufbaus (Stackup) ab, also von Breite, Höhe und Abstand der Leiterbahn zu einer als Rückstrompfad dienenden Referenzlage/-fläche. Auch die Di-Elektrizitätskonstante „ε“ des umgebenden Isolationsmaterials hat einen Einfluss auf das Impedanz-Verhalten.

Mit diesem Wissen ist es relativ einfach, die generellen Auswirkungen bestimmter physikalischer Konfigurationsänderungen auf die Impedanz-Werte der Leiterbahnen in Ihrer Tendenz vorherzusagen. Bei stark gekoppelten (=eng nebeneinander verdrahteten) Leiterbahnen und dem Einfluss des Ätzprozesses sowie der ‚Rauigkeit‘ des Kupfers wird eine exakte Bestimmung der Impedanz durch analytische Formeln jedoch eher ungenau. Hier sind numerische Werkzeuge (sog. Field-Solver, integriert z.B. in CR-8000 Design Force) dann essenzielle Werkzeuge für den High-Speed PCB Designer.

Leiterplattenentwickler sollten jedenfalls immer im Hinterkopf behalten, dass die Beziehung zwischen Kapazität und Impedanz in gewisser Weise invers ist. Das bedeutet, wenn „C“ steigt, sinkt der Wert von „Z0“ und umgekehrt.

Aber was bedeutet das genau für Stromversorgungsysteme (PDNs)? Diese bestehen typischerweise aus einer Kombination von flächigen Strukturen zusammen mit Leiterbahnen, Durchkontaktierungen, angeschlossenen aktiven Bauteilen (Verbrauchern), Energiequellen (Spannungsregler oder Power-Management ICs) und diskreten Komponenten im Pfad (Kondensatoren, Widerstände, Induktivitäten). Wie und wo kommt hier der Begriff Impedanz ins Spiel?

Einführung des Begriffes der PDN-Impedanz

Bei steigenden Takt- und Datenraten moderner High-Speed-Anwendungen und immer leistungsfähigeren ICs (CPUs, Microcontroller, DSPs oder FPGAs mit mehr als tausend Pins und mehreren hundert Stromversorgungspins) wird die Sicherstellung einer störungsfreien Stromversorgung von der Quelle (VRM, DC-DC-Wandler oder Power-Management-IC) zu allen Senken (Verbraucher-ICs) zu einer wesentlichen Herausforderung für jeden PCB Designer.

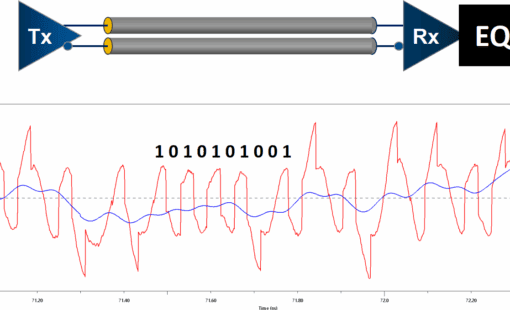

Wenn schnell schaltende aktive Bauteile (ICs) auf dem Board ihren Zustand ändern (typischerweise schalten immer viele I/Os eines ICs gleichzeitig), dann werden parasitäre (Schalt-)Ströme induziert und es entstehen Störspannungsspitzen. Diese können sich im gesamten Versorgungssystem ausbreiten und dann zu funktionalen Fehlern führen und zudem auch das EMV-Verhalten negativ beeinflussen.

Diese Störungen variieren in ihrem Auftreten sowohl räumlich auf der Platine (Ortsabhängigkeit) als auch über die Arbeitsfrequenz des Boards (Frequenzabhängigkeit). Aber wie wir bereits im Physikunterricht gelernt haben: „Energie verschwindet nicht!“. Daher beeinflussen diese Störung (=Energie) leicht alle umgebenden High-Speed-Funktionen auf dem Board. Störspannungen sind außerdem effiziente Quellen von EMV-Abstrahlung (sie bilden hochwirksame parasitäre EMV-Antennen).

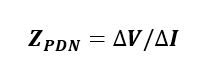

Im realen Betrieb mit anliegendem Spannungspegel und einem Stromfluss bildet das Verhältnis zwischen diesen Größen die Impedanz eines PDNs ab, wie in der Abbildung 1. Zur Vereinfachung ist im Bild nur die Flächenkapazität der Power-/Ground Planes dargestellt, ebenso sind die verschiedenen parasitären Induktivitäten nicht im Bild dargestellt.

Ein Ansatz zur Gewährleistung eines störungsfreien Betriebs von High-Speed-Baugruppen kann die Kontrolle der PDN-Impedanz über einen bestimmten Frequenzbereich sein. Dies erfordert eine sorgfältige Auslegung der PDN Struktur mit Berücksichtigung aller Kapazitäten und sämtlicher verschiedener Induktivitäten. Die PDN-Kapazität umfasst neben den Stütz- und Abblock-Kondensatoren auch die Plattenkapazität der Überlappungsbereiche der Kupferflächen von Power- und Ground. Zusätzlich fließen in beschränktem Umfang auch die in den IC-Gehäusen integrierten Kondensatoren und die sog. ON-DIE-Capacitance mit ein. Der naheliegende Formel-Ansatz für die PDN-Impedanz ist:

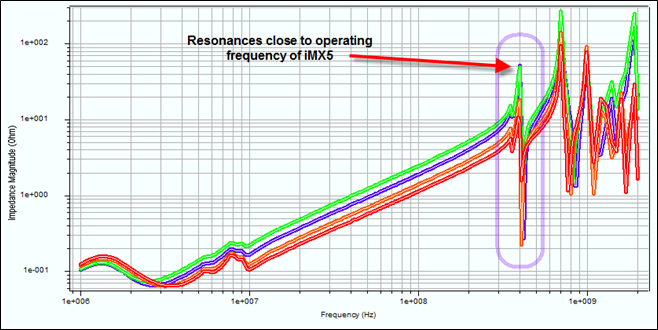

Wenn wir uns das Frequenzverhalten etwas genauer ansehen (siehe Abbildung 2), so wird ersichtlich, dass jedes PDN bei niedrigeren Frequenzen erst ein gewisses kapazitives Verhalten aufweist, während es sich dann durch die Vielzahl der verschiedenen Induktivitäten in Reihe dann in ein induktives Verhalten verändert.

Dieser Impedanz-Verlauf wird durch die physikalische Trennung der einzelnen Komponenten des PDNs innerhalb des PCB-Stackups beeinflusst. Bei steigender Frequenz führen die gekoppelten Induktivitäten der beteiligten Komponenten des PDNs zu einer Erhöhung der Impedanz. Oft weist dann die Impedanz einer Struktur mit sehr vielen Komponenten (=viele gekoppelte Induktivitäten) auch sehr viele Resonanzen und Antiresonanzen auf.

PDN-Design und Zielimpedanz

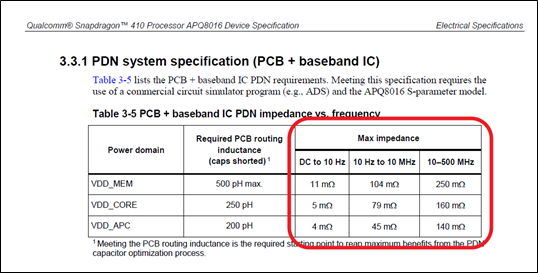

Das Wissen um die Zielimpedanz und die Kontrolle der Impedanzwerte über den Frequenzverlauf ist in den letzten Jahren zu einem Standardansatz für ein geeignetes PDN-Design geworden. Dies gilt insbesondere dann, wenn Designer die vorgegebenen Spezifikationen des IC-Herstellers erfüllen müssen. Die Zielimpedanz legt dann per Definition eine Grenze für den höchsten Impedanzwert fest, der das jeweilige Stromversorgungsnetz auf dem Chip in ihrer Verbindung zum PDN ausgesetzt sein sollte.

Der konkrete Wert der Zielimpedanz wird oft durch verschiedene Formelansätze definiert, die aber alle auf dem Ohm’schen Gesetz basieren. Dieses besagt, dass das Verhältnis aus Spannung zu Strom den Widerstand (=Impedanz) ergibt. Für ein PDN ist die Spannung in diesen Formeln die Versorgungsspannungsdifferenz (also ein ∆V) zum Nominalwert der Stromversorgung, welchen ICs akzeptieren können. Die IC-Hersteller verfügen natürlich über diese Informationen. In einer einfachen Form kann der Zielimpedanzwert beispielhaft durch folgende Formal definiert werden:

Somit kann eine Zielimpedanz als Obergrenze für das Strom-/Spannungsverhältnis verstanden werden, um so sicherzustellen, dass das ∆V nicht die erforderlichen Limits für die Störspannung überschreitet. Wenn die PDN-Impedanz unter diesem Wert bleibt, führt selbst eine maximale Energieanforderung des ICs nur zu einem eher geringen Einbruch der Versorgungsspannung und der sichere Betrieb ist gewährleistet.

Die Impedanzkurve sollte im Idealfall innerhalb des Frequenzbereiches, in dem die ICs Energie benötigen, flach und ohne Resonanzen bzw. Anti-Resonanzen sein. Der dafür relevante Frequenzbereich erstreckt sich in der Regel bis zu einigen Oberwellen der jeweiligen Taktfrequenz des ICs.

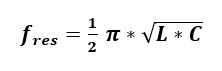

Dies ist das grundlegende Leitprinzip des Designansatzes für PDNs, welches mit einer Kontrolle der Zielimpedanz arbeitet. In einem PDN entsteht jede Resonanz durch sich ergebende parallele parasitäre RLC-Schaltungen. Die charakterisierenden Elemente solcher Resonanzen sind dabei:

- Die Parallelresonanzfrequenz

- Wellenwiderstand und Ausbreitungsgeschwindigkeit

- Die maximalen Impedanzwerte an den Resonanzstellen (es wird auf den Q-Faktor an dieser Stelle nicht eingegangen)

Die Parallelresonanzfrequenz ist die Frequenz, bei der induktive und kapazitive Reaktanz den gleichen Wert haben ist. Diese Frequenz kann berechnet werden aus:

Ein erhöhter Impedanzwert z.B. an einer Resonanzstelle ist ein Zeichen für einen potentiell zu hohen Störspannungswert mit entsprechenden negativen Folgen für Funktionalität und EMV-Verhalten. Erschwerend kommt hinzu, dass oft eine Vielzahl von Resonanz-Peaks (Mehrfachresonanzen und Antiresonanzen) in einem breiteren Frequenzbereich auftreten.

Nun bedeutet nicht jeder Impedanz-Peak, der den Zielwert der Halbleiter-Hersteller überschreitet, zwingend, dass das System nicht funktioniert. Allerdings können erhöhte Störspannungen dazu führen, das ICs während des Systembetriebs sporadisch ausfallen. Das öffnet dann schnell die „Büchse der Pandora“ in punkto Fehlersuche bei Hardwareausfällen. Aber selbst, wenn die Impedanzwerte unter den Impedanzgrenzen bleiben, kann es zu Problemen in der Energieversorgung kommen, so dass Gegenmaßnahmen oder Optimierungen erforderlich sein können.

Erste-Hilfe-Maßnahmen zur Senkung der PDN-Impedanz

Mit der oben skizzierten sog. FDTIM-Methode (Frequency-Domain-Target-Impedance-Method) soll sichergestellt werden, dass ein PDN-Design die gewünschten Vorgaben zur Zielimpedanz erfüllt und die Werte im relevanten Frequenzbereich unter den jeweiligen Grenzwerten bleiben.

Dies ist jedoch leichter gesagt als getan. Eine moderne High-Speed Leiterplatte (z.B. Automotive ECU) enthält in der Regel Dutzende von aktiven Komponenten, dazu meist mehrere Hundert Kondensatoren und Induktivitäten mit all ihren parasitären Eigenschaften (u.a. ESL und ESR der Kondensatoren). Außerdem treten weitere parasitäre Induktivitäten auf den verschiedenen PDN-Elementen (z. B. Pads/Land-Patterns, Durchkontaktierungen und Leiterbahnen) auf, die das PDN-Impedanz-Verhalten stark beeinflussen können.

Um die Impedanz des PDNs zu senken, können Ingenieure an zwei grundlegenden „Stellschrauben“ drehen: Eine Verringerung der Induktivität und/oder Erhöhung der Kapazität des PDNs. Die Platzierung und der Wert der Entkopplungskondensatoren spielen bei dieser Optimierung im höheren Frequenzbereich eine wichtige Rolle. Eine Platzierung der Kondensatoren auf der gleichen Ebene wie die IC-Versorgungspins würde beispielsweise die Induktivität minimieren, kommt jedoch aus Platz- oder Fertigungsgründen oft nicht in Betracht. Wenn aber bei einer PI-Analyse deutliche Resonanzen sichtbar werden, muss höchstwahrscheinlich auch die Kontur der größeren Kupferflächen der Spannungssignale modifiziert werden, um die Resonanzen vollständig zu entfernen.

Zuken PI/EMI-Tool und seine PI-Simulationsfunktionen zur Behandlung von PDN-Impedanz Fragestellungen

Angesichts der Komplexität heutiger PDNs und der Vielzahl potenzieller parasitärer Effekte ist die Analyse eines Layouts hinsichtlich der PDN-Impedanz leider kaum mit dem guten alten Stift und einem Blatt Papier zu bewerkstelligen. Außerdem können PCB-Design-Tools Impedanzvorgaben nicht einfach durch die Definition einer Designregel oder das Hinzufügen eines Attributs zu einem Stromversorgungsnetz abhandeln, auch wenn dies für den PCB-Designer vielleicht wünschenswert wäre.

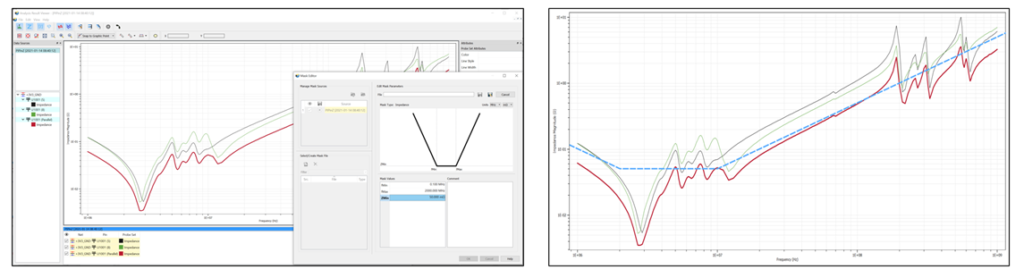

Stattdessen werden hochentwickelte Analyse-Werkzeuge wie z.B. numerische PI-Solver benötigt. Derartige Simulatoren sind seit vielen Jahren für PCB-Layouter verfügbar. Das PI/EMI-Tool von Zuken mit seinen dedizierten numerischen Solvern für DC- und AC-Power-Integrity incl. Impedanz- und Abblockungs-Analyse bietet einen einfach zu nutzenden Ansatz, um die verschiedenen Herausforderungen des Power-Integrity-Designs als integralen Teil des Entwurfsprozesses anzugehen.

Die Untersuchung und Überprüfung der PDNs ist während PCB-Designprozesses einfach möglich ohne komplexe Modellierungs- oder Schnittstellenprobleme zu externen Werkzeugen. Durch ein Absenken der Impedanzwerte des PDNs über den gesamten Frequenzbereich kann man auch potenzielle EMV-Probleme vermeiden.

Die wesentlichen Funktionen des Zuken PI/EMI-Tools sind:

- Überprüfung des Impedanz-Verhaltens und potenzieller Resonanzstellen der PDNs auf einem Board (incl. Vergleich mit Impedanzmasken die die IC Herstellervorgaben abbilden), des Stromverteilungssystems und Validierung dieser Werte anhand der Impedanzgrenzwerte der IC-Hersteller).

- Detaillierte Untersuchung der flächigen Impedanzverteilung für vom Anwender ausgewählte Frequenzen und an benutzerdefinierten Messpunkten (Ports).

- Lagenaufbau-Definition und Festlegung auf welchen Lagen das PDN verlegt wird bzw. Aufteilung in Teilbereiche mit unterschiedlichen Spannungen.

- Optimierung der Platzierung und Dimensionierung von Abblockkondensatoren um funktionale (aber auch kostenoptimierte) Designs zu erreichen, einschließlich einer Funktion zur Platzierung virtueller Kondensatoren für die Bewertung möglicher Designalternativen.

- Identifizierung von Hot-Spots im Hinblick auf erhöhte Stromdichten und Spannungsabfälle (IR-Drop).

- Analyse der Durchkontaktierungen der PDNs in Punkto maximale auftretende Ströme und IR-Drop, einschließlich What-If-Analysen (weitere Informationen finden Sie in diesem Artikel zum Thema Power Integrity).

Wenn eine solche PI-Analyse Resonanzen in Ihrem PDN aufzeigt, können notwendige Korrekturen in durch parametrische Untersuchungen am virtuellen Prototyp (Digital Twin) ausgearbeitet werden. Das kann z. B. das Hinzufügen von virtuellen Abblockkondensatoren sein oder das Ändern von Bauteil-Werten und Package-Dimension oder z.B. ESL der Kondensatoren. Sogar das interaktive Ein-/Ausschalten derselben ist möglich, ohne dass konkrete physische Designänderungen im PCB-Tool erforderlich sind.

Dank der schnellen Simulations-Engine (frequency domain) können PCB Designer Änderungen des Impedanz-Verhaltens quasi im Handumdrehen ausarbeiten. Der eingebettete DC-Solver ermöglicht auch die Visualisierung des Stromflusses innerhalb des PDNs für detaillierte Untersuchungen direkt im ECAD-Tool.

Zusammenfassung

Der Ansatz einer entwurfsbegleitenden Power Integrity-Analyse kann PCB-Entwicklern dabei helfen, ein Over-Engineering des PDNs zu vermeiden. Eine zu defensive Herangehensweise führt oft dazu, dass z.B. redundante Kondensatoren zum PDN hinzugefügt werden und am Ende des Design Prozesses zusätzliche Validierungsarbeit anfällt, und damit unnötige Kosten entstehen.

Und zu guter Letzt noch zur Erinnerung: Erfahrende Elektronikentwickler wissen, dass die Realität eines Layouts häufig noch drastischere Anwendungs-Szenarien mit sich bringt als erwartet (Stichwort: Murphy‘s Law). Dies gilt auch für Power Integrity-Probleme wie Resonanzen von Impedanz-Verläufen. Diese beeinträchtigen auch signifikant das Signal Integrity-Verhalten von Leiterplatten, und ein PDN kann in seinen Eigenschaften (von der physischen Dimension der Struktur her als recht großer LC-Resonator leicht zu einer effizienten parasitären EMV-Antenne werden. Das unterstreicht, wie wichtig es ist, die Power Integrity und die Impedanz eines PDNs unter Kontrolle zu halten.