High Speed Links und die SI-Grundlagen neu betrachtet

Das Design von High-Speed-Serial-Links vermittelt Designern oft das Gefühl, dass die Zeiten, in denen Signalintegrität gleichbedeutend mit schwarzer Magie war, wiederkehren. Schließlich steigen die Datenraten unaufhaltsam. Ein kürzlich geführtes Gespräch zwischen Donald Telian von SI Guys und Ralf Brüning bringt die Diskussion zu den Grundprinzipien zurück. Wenn ihr die wichtigen Prinzipien kennt, wird SI zu einer verständlichen Ingenieursdisziplin.

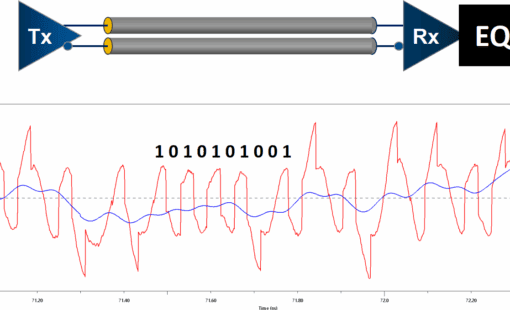

Für diejenigen unter euch, die nicht täglich mit Hochgeschwindigkeitsverbindungen und SerDes zu tun haben: Serializer/Deserializer (SerDes) bezeichnet eine Datenübertragungstechnologie, die in der modernen Hochgeschwindigkeitskommunikation eingesetzt wird, um die Grenzen früherer Datenübertragungsmethoden zu überwinden.

Der Hauptzweck eines SerDes besteht darin, die Datenübertragung über eine einzige Leitung oder ein Differentialpaar zu ermöglichen, um die Anzahl der I/O-Pins und Verbindungen zu minimieren. SerDes-Verbindungen sind die primäre Lösung, die in allen Hochgeschwindigkeitsschnittstellen wie PCIe, Ethernet, SATA, HDMI, Display-Port, Fast USB und vielen anderen verwendet wird.

Die gute Nachricht ist, dass alle Sarial Links elektrisch gesehen gleich sind. Praktisch gesehen kommt es bei zuverlässigen Verbindungen darauf an, Verluste und Diskontinuitäten zu verstehen und zu beherrschen. So können beispielsweise selbst kurze Stubs in der Nähe der Viertelwellenlänge katastrophale Auswirkungen haben, und Reflexionen von kleinen Strukturen (z. B. Durchkontaktierungen) verursachen Intersymbolinterferenzen (ISI), die die Signalintegrität beeinträchtigen.

Infolgedessen setzen moderne Empfänger zunehmend auf Entzerrung, um dieses Problem zu bewältigen. Dieser Blogbeitrag und insbesondere Dons LIVE Gen2 SI-Kurs in München bringen diese Aspekte für Elektronikentwickler, die keine SI-Spezialisten sind, auf den Punkt und zeigen, wie man mit dem richtigen Ansatz Probleme vermeiden und erkennen kann, bevor sie im Labor auftreten.

Signal Integrity Unplugged: An Expert-to-Expert Conversation (20 min)

Verlust vs. Diskontinuitäten: zwei verschiedene Arten, ein Signal zu verlieren

Jede Highspeed-Verbindung weist ein gewisses Verlustverhalten auf, sodass ein Teil der übertragenen Energie nicht beim Empfänger ankommt. Dieser Verlust ist eine vorhersehbare Dämpfung, die durch die Konfiguration des Kupfers und des Dielektrikums verursacht wird. Sie reduziert die Signalamplitude mit zunehmender Frequenz und Übertragungsentfernung stetig.

Diskontinuitäten wie Durchkontaktierungen, Pads, Steckverbinder oder abrupte Stapel- oder Geometrieänderungen verursachen Impedanzfehlanpassungen. Diese reflektieren einen Teil der Energie zurück zur Quelle. Diese Reflexionen überlagern nachfolgende Bits und schließen das Auge auf eine Weise, die nicht immer durch Entzerrung entwirrt werden kann.

Ein guter erster Schritt in jedem Projekt ist es deshalb, das primäre Problem in Ihrer Verbindung zu identifizieren. Lange Backplanes oder Kabel sind oft verlustbehaftet (konzentrieren Sie sich auf Materialien, Länge und Ausgleichsspielraum). Kurze, modulare Verbindungen mit mehreren Übergängen sind dagegen in der Regel reflektionsbehaftet (suchen und beseitigen Sie zuerst die Fehlanpassungen). Eine sorgfältige Budgetplanung und etwas detektivische Arbeit sind hier der Schlüssel zum Erfolg!

Deswegen sind Stubs das „Schreckgespenst“ (insbesondere nahe der Viertelwellenlänge)

Ein Stub ist jeder nicht terminierte Abzweig von Ihrem Hauptpfad, beispielsweise eine Verzweigung, ein ungenutzter Teil eines Via-Barrels oder ein verbleibendes Testpad. Bei niedrigen Frequenzen kann ihre Wirkung oft ignoriert werden, während sie bei hohen Frequenzen Ihr Signal unterdrücken kann. Nähert sich die Länge eines Stubs bei energietragenden Frequenzen λ/4 (einem Viertel der Wellenlänge), ist die vom offenen Ende zurückkehrende Reflexion um fast 180° phasenverschoben.

Dies kann das Hochfrequenzsignal auf Ihrem Hauptpfad auslöschen. In der Praxis bedeutet dies, dass die Aughöhe zusammenbricht, obwohl der physikalische Stub „kurz” aussieht. Mit steigenden Datenraten werden Stablängen, die früher keine Rolle spielten, plötzlich wichtig. Telians „SI-Spickzettel” hilft Ihnen zu verstehen, was wann wichtig ist. Die Lösung ist einfach, aber unumgänglich: Entfernt oder verkürzt die Stäbe (z. B. durch Rückbohren ungenutzter Durchkontaktierungen, Auswahl von Schichtpaaren, die die Durchkontaktierungslänge minimieren, oder Vermeidung von Streuzweigen und Testpads in Hochgeschwindigkeitsnetzen). Behandelt Stäbe bei Designprüfungen außerdem als risikoreiche Elemente.

Reflektionen, ISI und die Bedeutung der Impedanzkonsistenz

Reflektionen verringern nicht nur die Amplitude, sondern verschmieren auch die Zeit. Echos treten als zusätzliche Unebenheiten nach einem Übergang auf und gehen in die nächsten Einheitenintervalle über. Dieser Effekt wird als ISI bezeichnet.

Je näher eine Diskontinuität am Sender oder Empfänger liegt, desto größer ist ihre Auswirkung. Das Gegenmittel klingt vielleicht langweilig, ist aber sehr wirkungsvoll: Die Impedanz von Die-Pad zu Die-Pad sollte konstant gehalten werden. Package-Ausbrüche, Geometrie, Steckverbinderanschlüsse, Leiterbahnbreite/-höhe und Stack-übergänge sollten wie eine durchgehende Übertragungsleitung behandelt werden.

Wenn eine Änderung erforderlich ist (Schicht, Medium oder Geometrie), gestaltet den Übergang sanft und bewusst statt abrupt und zufällig. Und wenn ihr aus irgendeinem Grund mit der Impedanz eines bestimmten Merkmals nicht weiterkommt, findet ihr in den Artikeln von Telian im SI Journal sieben weitere Möglichkeiten, mit eurer Diskontinuität umzugehen.

Impedanzanpassung: Mit modernen Tools kein Rätselraten mehr

Das Erreichen einer konsistenten Impedanz und minimaler Diskontinuitäten klingt zwar arbeitsintensiv, ist mit modernen PCB-Tools aber durchaus zu bewältigen. In der richtigen Umgebung kannst du die Impedanz von Leiterbahnen bzw. den Lagenaufbau im Voraus planen und die Ergebnisse während des Layouts überprüfen. So erkennst du Probleme bereits vor der Fertigung.

Zuken CR-8000 Design Force enthält einen integrierten EM-Feldlöser für die Planung der Leiterbahn-/Stapelimpedanz sowie TDR-ähnliche Impedanzprüfungen während des Layouts. Wenn du eine detaillierte 3D-Via-Charakterisierung benötigst, kannst du Design Force mit Partnerlösungen (z. B. Ansys oder Keysight) verbinden, um beispielsweise die Auswirkungen von Via-Geometrien zu analysieren und zu minimieren.

In der Vergangenheit haben viele Teams die Auswirkungen der Durchkontaktierungen übersehen und nur die Leiterbahnbreiten berücksichtigt. Bei Geschwindigkeiten über ~10 Gb/s werden durchkontaktierungsbedingte Reflektionen in Standard-Leiterplatten deutlich. Durch die Impedanzplanung im Fluss in Kombination mit einer gezielten 3D-Analyse können Sie Bohrdurchmesser, Pads, Rückleitungs-Durchkontaktierungen und Anti-Pads so abstimmen, dass Reflexionen an den entscheidenden Stellen reduziert werden.

Daraus ergibt sich ein pragmatischer Arbeitsablauf: Simuliert frühzeitig, um zu entscheiden, ob eure Verbindung verlust- oder reflektionsbegrenzt ist. Behebt anschließend die physikalischen Ursachen (z. B. Entfernen von Stubs, Abflachen von Starts, Optimieren des Stackups) und wendet erst dann die richtige Entzerrung an. Enge Design-Analyse-Schleifen verkürzen die Zeitpläne und verhindern teure Neukonstruktionen.

Der Aufstieg von Rx Equalization – und was es uns sagt

Heutige Empfänger verfügen über immer leistungsfähigere Equalizer, insbesondere über längere DFE-Tap-Ketten (Decision Feedback Equalizer), mehr CTLEs und sogar FFEs. Dies ist ein Symptom dafür, dass Kanäle mehr ISI über mehr Einheitenintervalle übertragen. Das zeugt von beeindruckender Siliziumtechnik, ist aber kein Grund, bewährte Layout-Praktiken zu ignorieren. Zunächst werden robuste Verbindungen in Kupfer aufgebaut und dann in Silizium fertiggestellt, nicht umgekehrt.

Was bedeutet das für unseren Arbeitsalltag?

Bei allen Designprojekten sind die Grundlagen entscheidend. Beginne deine Entwürfe, indem du Risiken als Verluste oder Diskontinuitäten klassifizierst. Behandle Stubs als Show-Stopper. Nutze Impedanzplanung und TDR-Prüfungen im Fluss, um die Impedanz konsistent zu halten. Verwende den Ausgleich zum Polieren, nicht zur Rettung. Wenn du diese Reihenfolge befolgst, verbringst du weniger Zeit im Labor, erzielst schnellere Inbetriebnahmen und vermeidest „mysteriöse” Ausfälle in späten Testphasen.

Nächste Schritte und weitere Ressourcen

- Weitere Informationen zum Thema findest du im vorherigen Artikel dieser Serie:

- Nimm an einem Experten-Training teil. Wenn du praktische Kenntnisse über herstellerneutrale Best Practices erwerben möchtest, besuch Donald Telians LIVE-Kurs „Signal Integrity, in Practice” Gen2 SI Class in München (29.–30. Oktober 2025). Hier lernst du, wie du diese Prinzipien in wiederholbare Labor- und Layout-Gewohnheiten umsetzen kannst. Melde dich an unter www.siguys.com/training

CR-8000 für High-Speed Design

- Erfahre, wie CR-8000 Design Force SI Advance das constraint-gesteuerte Layout, SI-Prüfungen während des Designs und 3D-Co-Design unterstützt, um Diskontinuitäten zu minimieren.

- Schaut euch eins unser On-Demand-Webinare zum Thema High-Speed-Design aus unserer Signal Integrity/Simulation Webinar Library an.

Fazit

Auch wenn die Leitungsgeschwindigkeiten steigen, bleibt der Weg zu zuverlässigen Verbindungen derselbe: Zuerst die Kupferleitung reparieren, dann mit Silizium abschließen. Durch bewusste Vermeidung von Verlusten und Diskontinuitäten, Eliminierung von Viertelwellen-Stubs, Durchsetzung einer konsistenten Impedanz und Verwendung einer gerechten Entzerrung liefert ihr sauberere Designs mit weniger Überraschungen. Moderne, analysefähige PCB-Tools – unterstützt durch gezieltes Training – erleichtern die Anwendung dieser Grundlagen Tag für Tag.