The industry’s shift toward high-speed designs is evident everywhere. We can see it in motor control units (ECUs), in IoT technology, or in next-generation wireless communication devices. This shift defines new design challenges for PCB design engineers. In particular, the power distribution system behaviour of such a high-speed PCB, its parasitic effects, and the ability to predict its behaviour become a serious bottleneck in achieving high operating speeds. These issues are addressed to various extents in most PCB design flows by adding power-integrity simulation capabilities to the process.

When using complex numerical analysis tools, industrial users face three major concerns: accuracy, ease of use in the process, and overall performance/computing speed. Any CAD simulation software must overcome these concerns, and so must the solvers in the Zuken PI/EMI analysis environment CR-8000. The 2022 Release includes a new feature that will boost the performance of power integrity analysis through the use of multi-threading technology.

Zuken technology empowers growing PCBs

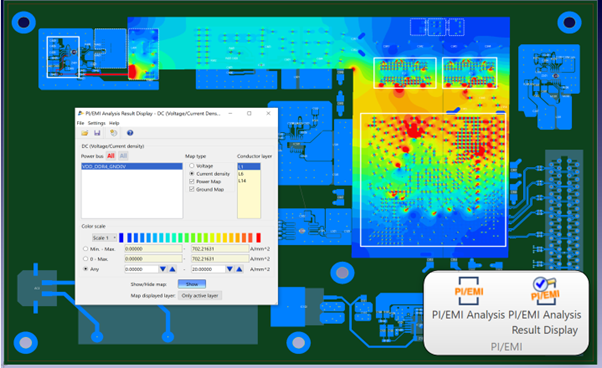

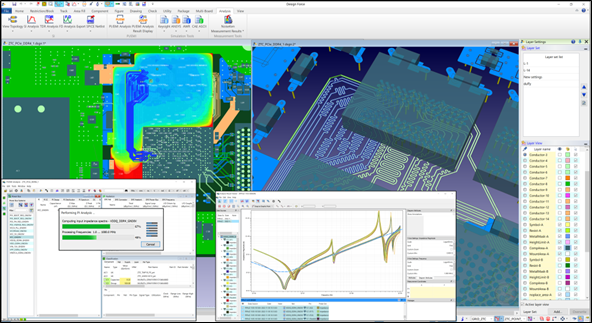

Zuken’s power integrity solution is remarkably user-friendly in its architecture, providing power integrity results such as IP-Drop quantities (e.g., current- and voltage-distributions) targeting potential trouble areas directly in the PCB design canvas with just a few clicks. The analysis speed of Zuken’s hybrid solver approach is also excellent compared to full-wave 3D-EM simulation approaches for this type of problem. In addition, the simulator is not impairing analysis accuracy at all and has been proven to produce good result correlations (see [1] for reference).

Although the smart hybrid frequency domain solvers employed by the Zuken PI analysis already outperform most other PI simulation approaches, users are constantly expecting improvements as the boards subject to analysis continuously grow bigger (up to more than 18 layers, containing multiple power-plane pairs, dozens of power-rails and thousands of components where the majority often are decoupling capacitors eating up the PCB real estate).

There is a requirement to accelerate simulation performance by using the full processing power of modern multi-core CPUs. Therefore, it was obvious for Zuken’s R&D team to run some of the analysis processes in parallel.

The science behind the new feature

Parallel programming in general is a widely used concept with different implementation concepts. It can either describe complete processes ( -> multiprocessing) or only subtasks running distributed and/or parallel on the same machine or even on different machines (in that case often part of high-performance-computing attempts, HPC). Multi-threading as a mechanism refers to the simultaneous execution of multiple sequential groups of CPU instructions forming a so-called thread. These threads could run on a single processor or even in one of the multiple kernels or cores of modern processors. In fact, rather is not actually running instructions in parallel, but is permanently switching fast and efficiently between the different tasks by using an intelligent scheduling algorithm.

Intel introduced the hyper-threading (an Intel trademark) technology a couple of years ago, which allows a single processor to operate like two separate virtual processors for the operating system and for the applications and programs using it. The physical processor is divided into two logical or virtual processors and improves the performance of the CPU. Hyper-threading technology allows multiple threads to run on each core of a CPU. As IC manufacturers added more and more cores to CPUs, more instructions can be executed simultaneously by such a CPU at a time. Each physical core is then recognized by the operating system as two virtual (or logical) cores. A single processor can run two threads independently.

Made for parallel processing

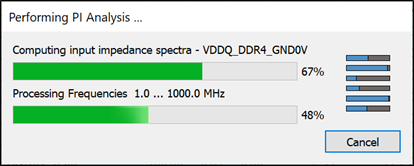

The new multi-threaded software architecture of our PI/EMI analysis tool uses the hyper-threading architecture and separates different analysis tasks into sub-processes and threads, which are then executed, dispatched, and scheduled independently. Because power integrity analysis takes place in the frequency domain, it lends itself quite well to parallel processing, since each calculation per frequency can be performed individually by processing the other frequencies of interest.

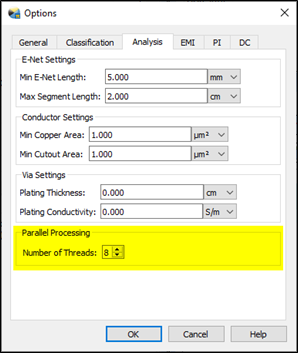

The user can set the number of allowed parallel threads under Options -> Analysis (to leave some CPU resources for other tasks like Microsoft Office, if desired). This number is limited to the number of the CPU cores or, in the case of a hyper-threading-enabled CPU, to twice the number of the CPU cores. The same applies to AMD’s so-called ‘Simultaneous Multithreading’ equivalent.

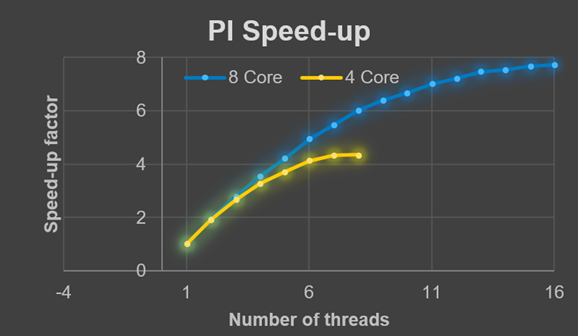

The achievable speed is more or less linear to the number of cores (threads) you free up to be used by the simulator (up to a certain saturation point of course).

The PDN shown below (a board comprising an Intel Arria © FPGA with 2 DDR4 memories, simulation of the DDR4 core voltage) illustrates the impact on the simulation performance with real numbers. The computing time on my Dell Intel i9 laptop system with 8 cores (32GB main memory, 64bit Windows10) reduces from 3 minutes down to 20 sec when all threads are activated. This defines a serious improvement in the analysis efficiency, especially when evaluating different design alternatives for the PDN structure.

CR-8000 includes fully integrated signal integrity analysis and power integrity simulation tools to verify all aspects of your single or multi-board PCB designs.

References:

[1] Brüning, Ralf, Kakerow, Ralf, Wagner, Torsten.; ” A Multistage ‘Power Integrity Surgery’ for the Design of Complex Automotive Electronic Control Units”, IEEE EMC&SI Symposium 2015, Santa Clara, CA, USA March 2015

- Blog

AI in PCB design is increasingly seen as a game-changer, with some predicting it could soon replace entire layout teams—but this view risks overlooking both the current limits of AI and the critical expertise engineering demands. At DesignCon 2025, experts from emphasized that AI's real value lies in complementing human judgment, not replacing it. Read more on our blog.

- Blog

Our new post explores the potential of augmented reality (AR) to transform everyday experiences in shopping, education, and navigation. It highlights how enhanced AR devices will offer immersive, interactive environments that blend the virtual and physical worlds.

- Blog

The field of PCB design continues to evolve as advancements in technology and shifting market demands push the boundaries of what’s possible. By 2025, several key trends are set to shape the industry. Find out more on our blog.

- Blog

Supply chain risk management is critical for electronics design. By integrating SiliconExpert with CR-8000, engineers gain tools to streamline component selection, manage obsolescence, and ensure design continuity. This integration supports efficient workflows, reduces costs, and mitigates supply chain disruptions.