Register to attend Zuken’s presentation at SemIsrael Tech Webinar

SemIsrael Tech Webinar 2022 brings together 16 expert presentations, various topics, live Q&A. One of those webinars is a presentation by Zuken expert Nikola Kontic

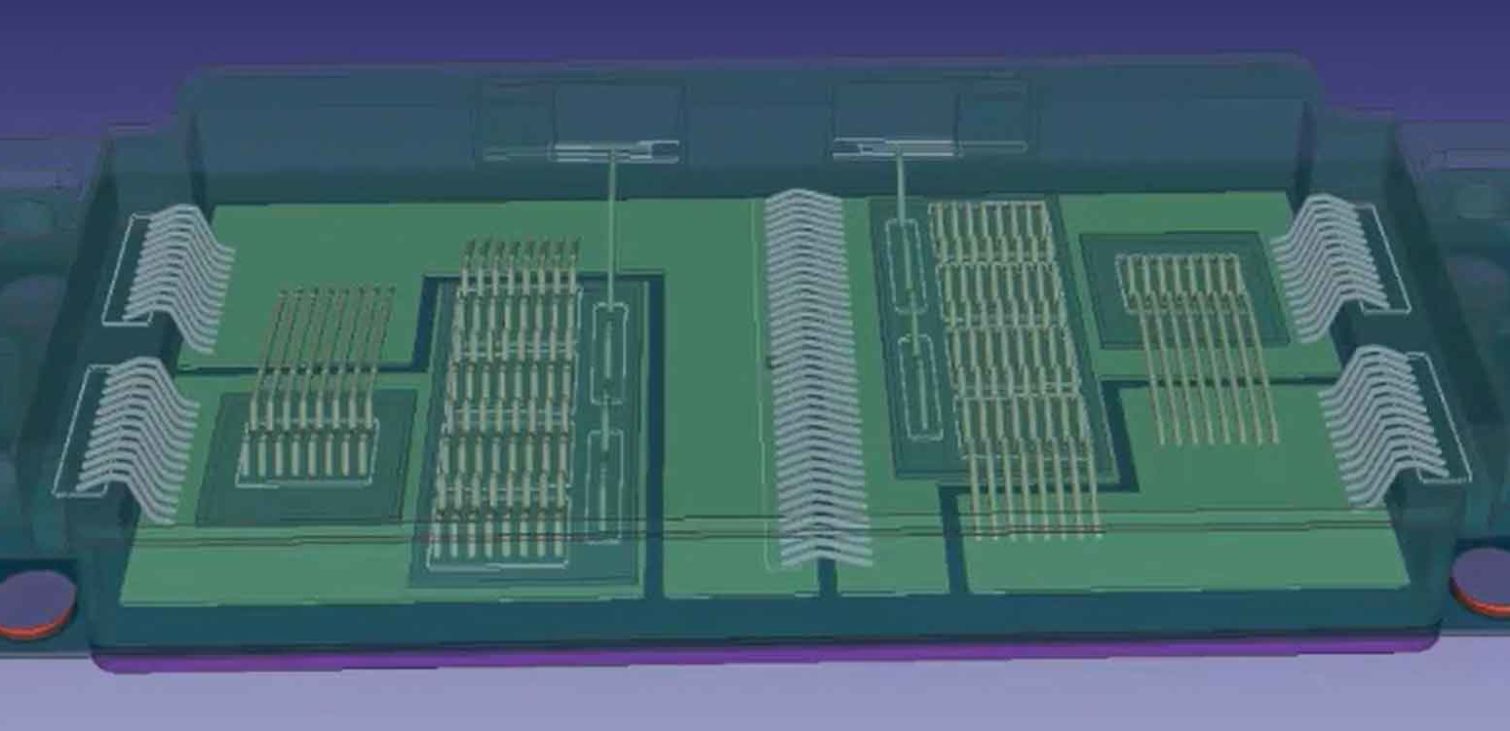

An Efficient Design Flow For IC Power Module Design

Physical Design Track 13:45 – 14:15 (UTC +2)

Power modules typically include several semiconductor devices on a PCB within a physically constrained enclosure. These power modules are typically soldered or sintered on a substrate that provides electrical and thermal contact and electrical insulation where needed.

Compared to discrete power semiconductors in plastic housings, power packages provide a higher power density and are in many cases more reliable. The typical power module design flow is in MCAD, where a just structural analysis, but no electrical analysis is performed. Combining electrical and mechanical power module designs in CR-8000 Design Force can enable additional electrical analysis and identify issues that would not be found in the structural analysis.

What you will learn

- Overview of the Power Module Market

- Current power module design flow for the challenges and issues faced in the design process

- Types of features and functions within the design element

- Introduction of an enhanced power module design flow using CR-8000 Design Force, including the features and benefits of this new design approach.

The presenter: Nikola Kontic

Nikola has worked at Racal Redac and now Zuken for more than 33 years. Experience has been gained in all global markets from USA, EU and Japan in the area of PCBs, Packaging for various electronic product designs. Formerly a Product Consultant at Zuken, Nikola presented at many event worldwide both Zuken and general electronic/EDA market. Sharing his experience and knowledge of the EDA market and technology trends and future direction. Also involved in many EU and UK funded projects has helped to introduce new design processes, design practises and help to evolve the EDA solution. Nikola’s current role involves introducing Zuken solutions to the engineering community across Europe, and he also contributes to the strategic direction of electronic product design solutions within Zuken.

Contact

If you have any questions, please contact the Zuken event manager Francesca Libe. Email: francesca.libe@it.zuken.com