Rafforza la qualità dei design high-speed già nelle fasi iniziali, evita rilavorazioni e mantieni un workflow semplice e affidabile.

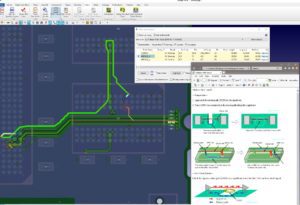

La progettazione di elettroniche ad alta velocità affidabili parte da layout che garantiscono segnali puliti, alimentazioni stabili ed emissioni controllate. Con l’aumento dei data rate e la crescente densità delle schede, anche piccole decisioni di instradamento possono trasformarsi in problemi EMC o in violazioni SI/PI durante i test. EMC Adviser EX ti offre un modo rapido, basato su regole, per intercettare questi problemi in anticipo. Analizza il progetto alla ricerca di pattern di layout che generano emissioni, degradano la qualità del segnale o riducono la power integrity. Ottieni indicazioni pratiche direttamente nell’ambiente di layout, senza configurazioni complesse o lunghi cicli di simulazione. Questo ti aiuta a sviluppare schede più robuste ed evitare spiacevoli sorprese nelle fasi finali del design.

Rafforza la qualità dei design high-speed già nelle fasi iniziali, evita rilavorazioni e mantieni un workflow semplice e affidabile.

Applica regole SI/PI/EMC unificate per evidenziare routing, cambi di layer e scelte PDN che generano jitter, rumore o emissioni.

Rileva problemi EMC critici come antenne parassite, ritorni di segnale interrotti, variazioni di impedenza e geometrie ad alta accoppiamento.

EMC Adviser EX analizza il tuo design alla ricerca di problemi come antenne parassite, discontinuità nelle schermature, percorsi di ritorno interrotti, variazioni di impedenza e geometrie ad alto accoppiamento. Questi controlli ti aiutano a individuare le strutture che generano emissioni, introducono jitter e riducono i margini di rumore con l’aumentare dei data rate.

Il set di regole copre aspetti di SI, PI ed EMC, offrendoti una visione chiara dei rischi di layout già nelle prime fasi del design. Identificando pattern di routing, transizioni di layer e scelte di distribuzione della potenza che causano radiazioni indesiderate o degradazione del segnale, lo strumento ti aiuta a realizzare design high-speed più puliti e robusti senza aggiungere complessità al workflow.

EMC Adviser EX offre analisi che vanno oltre i controlli classici sulla scheda a circuito stampato, collegando il comportamento elettrico al contesto meccanico 3D del prodotto. Il sistema identifica strutture parassite, discontinuità nelle schermature, problemi nei percorsi di ritorno e rischi di suscettibilità dovuti a campi esterni e ai concetti di massa adottati.

I risultati delle verifiche elettromeccaniche sono disponibili direttamente nell’ambiente di layout 3D, così i team possono verificare le contromisure, adattare le caratteristiche del contenitore e affinare il routing senza dipendere da solver esterni o da una complessa preparazione dei modelli. Il risultato è una visione più chiara del comportamento EMC nelle prime fasi di progettazione, che consente decisioni di sviluppo più consapevoli.

Le verifiche sulle antenne parassite identificano le tracce e le geometrie di rame che, alle alte frequenze, irradiano in modo indesiderato, contribuendo così a prevenire problemi di emissione già nelle prime fasi del layout.

Le analisi di schermatura e le verifiche basate su regole valutano la qualità e la continuità della schermatura all’interno dell’intero design, contribuendo a prevenire accoppiamenti indesiderati, emissioni e l’ingresso di disturbi esterni.

Le verifiche dei percorsi di ritorno assicurano che i segnali ad alta velocità mantengano un percorso di ritorno continuo e a bassa induttanza su tutti i layer e attraverso più schede.

Le verifiche di integrità del segnale valutano le condizioni fisiche che influenzano impedenza, riflessioni, timing e la qualità delle coppie differenziali nelle reti ad alta velocità.

Le verifiche sul crosstalk identificano le condizioni di routing e di PDN che amplificano l’accoppiamento indesiderato tra segnali e reti di alimentazione, sia in sistemi a singola scheda sia in architetture multi-board.

Le verifiche di power integrity garantiscono un’alimentazione stabile valutando il posizionamento dei condensatori di disaccoppiamento, la geometria del PDN, le interfacce dei connettori e i percorsi di corrente.

EMC Adviser EX integra i seguenti prodotti

In our webinar we will provide an introduction to the challenges of signal integrity and the underlying physical effects. This will provide the basis for practical tips to address the related challenges during PCB design.

DDR5 is the latest generation of memory. In this joint webinar with Keysight Technologies, we’ll begin with pre-layout simulation, then transition to CR-8000. The design will then be verified by Electromagnetic (EM) simulation and system simulations in Keysight ADS, in order to build confidence in the final DDR5 design.