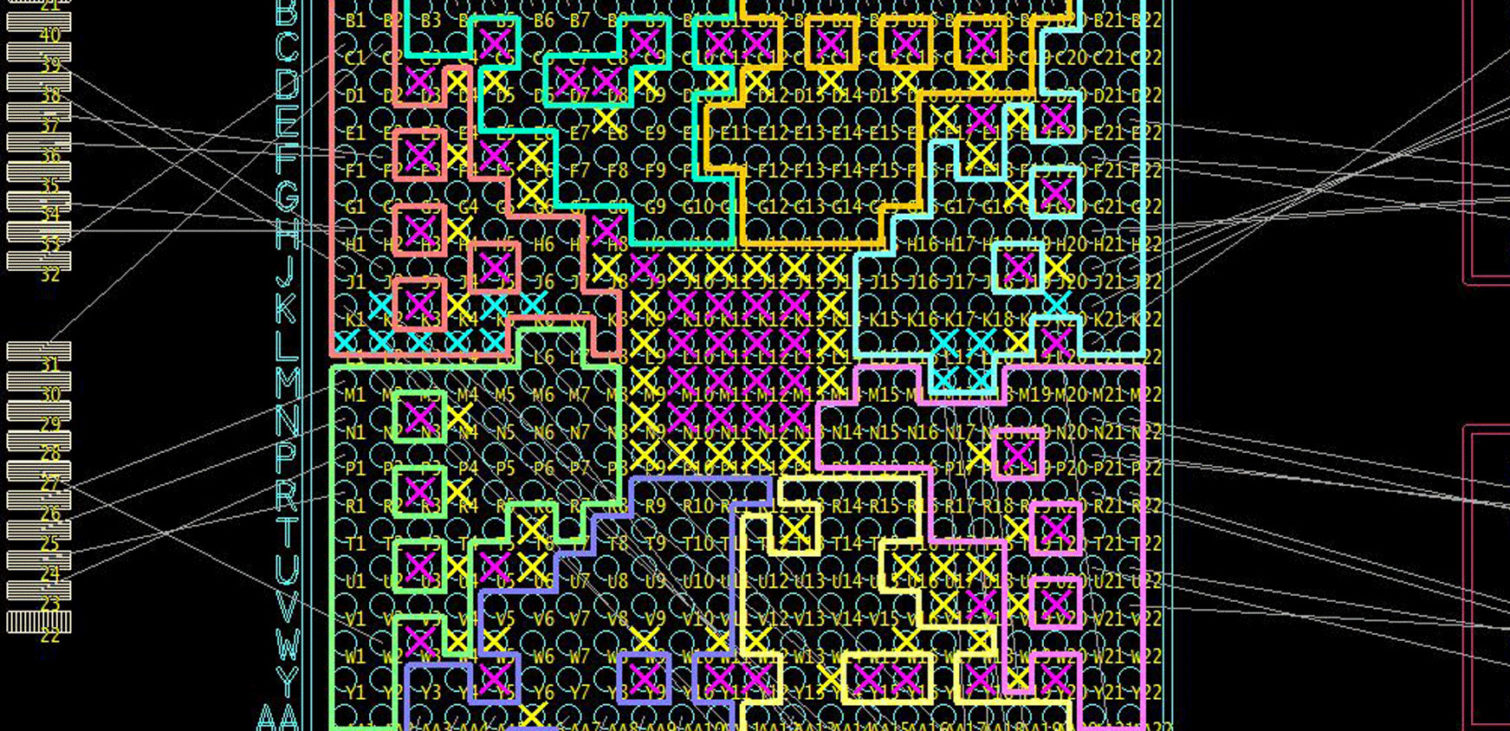

CR-8000 Graphical Pin Manager

Il Graphical Pin Manager (GPM) di Zuken offre un efficace ambiente di co-design FPGA/PCB che fornisce supporto per i dispositivi più recenti offerti dai fornitori di FPGA, come Xilinx, Intel, Lattice e Microsemi. Come parte della famiglia CR-8000, GPM consente ai team di progettazione di comunicare I/O e limitare le informazioni in modo intelligente per FPGA o altri dispositivi ad alto numero di pin, in qualsiasi momento, utilizzando Design Gateway e Design Force. Ciò significa che i dispositivi programmabili possono essere sviluppati in parallelo alla progettazione del PCB e sono pronti a soddisfare i tempi di consegna del progetto e di produzione.