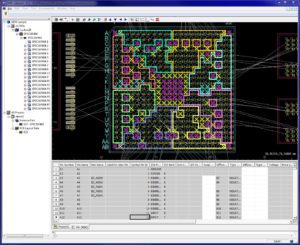

CR-8000 Graphical Pin Manager

Zuken’s Graphical Pin Manager offers an effective FPGA/PCB co-design environment providing support for the latest devices offered by FPGA vendors, such as Xilinx, Intel, Lattice, and Microsemi.

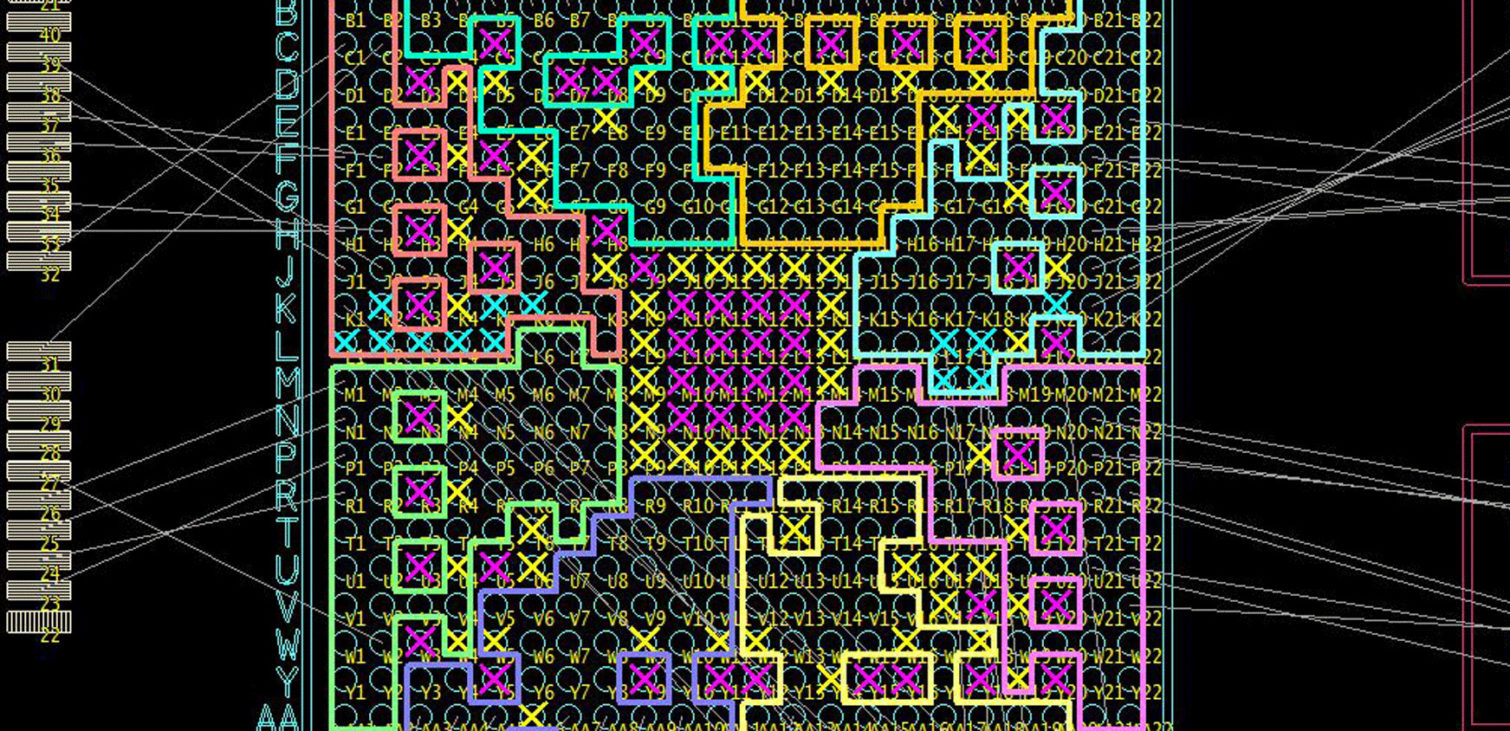

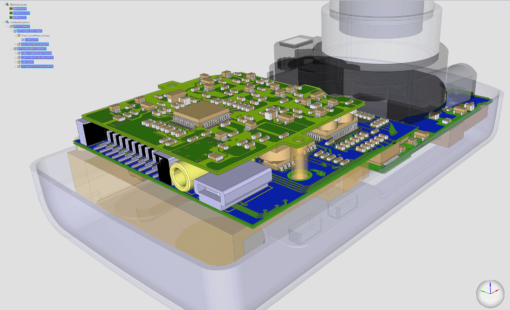

As part of the CR-8000 family, Graphical Pin Manager enables design teams to communicate I/O and constraint information intelligently for FPGAs or other high-pin count devices, at any time, using Design Gateway and Design Force. This means programmable devices can be developed in parallel to the PCB design, and are ready to meet project delivery and production schedules.