MultiCore CPU support for ultra-fast simulation performance.

Design Force SI Advance combines a range of new functionalities to enhance your signal integrity analysis capabilities. This new, comprehensive bundle covers all aspects of Signal Integrity from Characteristic Impedance to IBIS AMI analysis of SerDes channels.

MultiCore CPU support for ultra-fast simulation performance.

64-bit computing architecture for large data records and to support parallel processing

AI/ML-assisted S-Parameter modeling

Our suite of powerful tools offers a host of benefits to ensure your electronic projects thrive, optimizing signal integrity in every step of the design process.

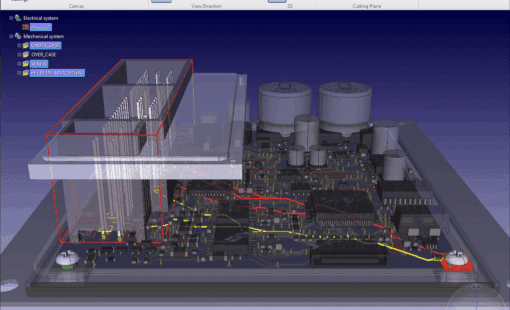

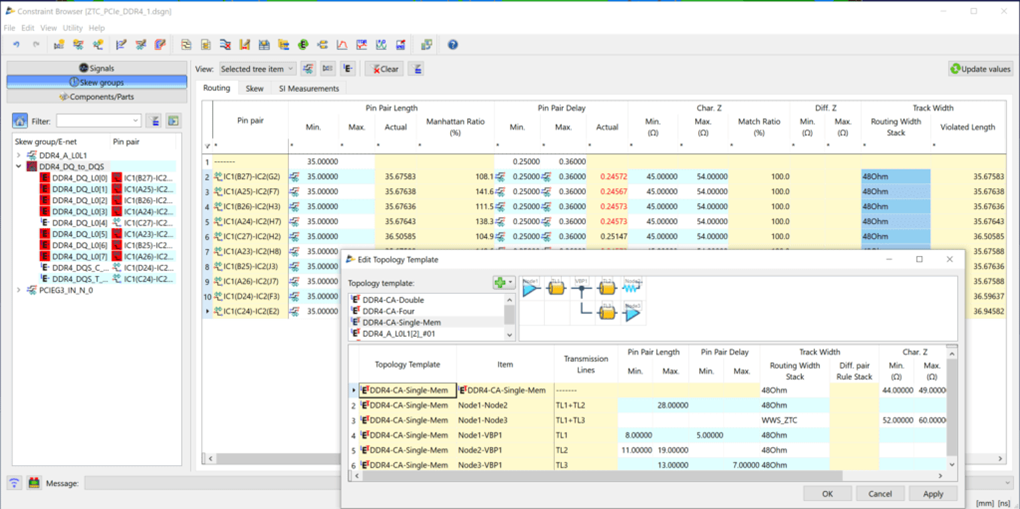

In the essential pre-layout phase, you are recommended to define the relevant high-speed constraints and to optimize the topology of critical nets (e.g.; double data rate signals). This early planning sets the stage for a robust physical design, reducing costly errors downstream and ensuring your project stays on track.

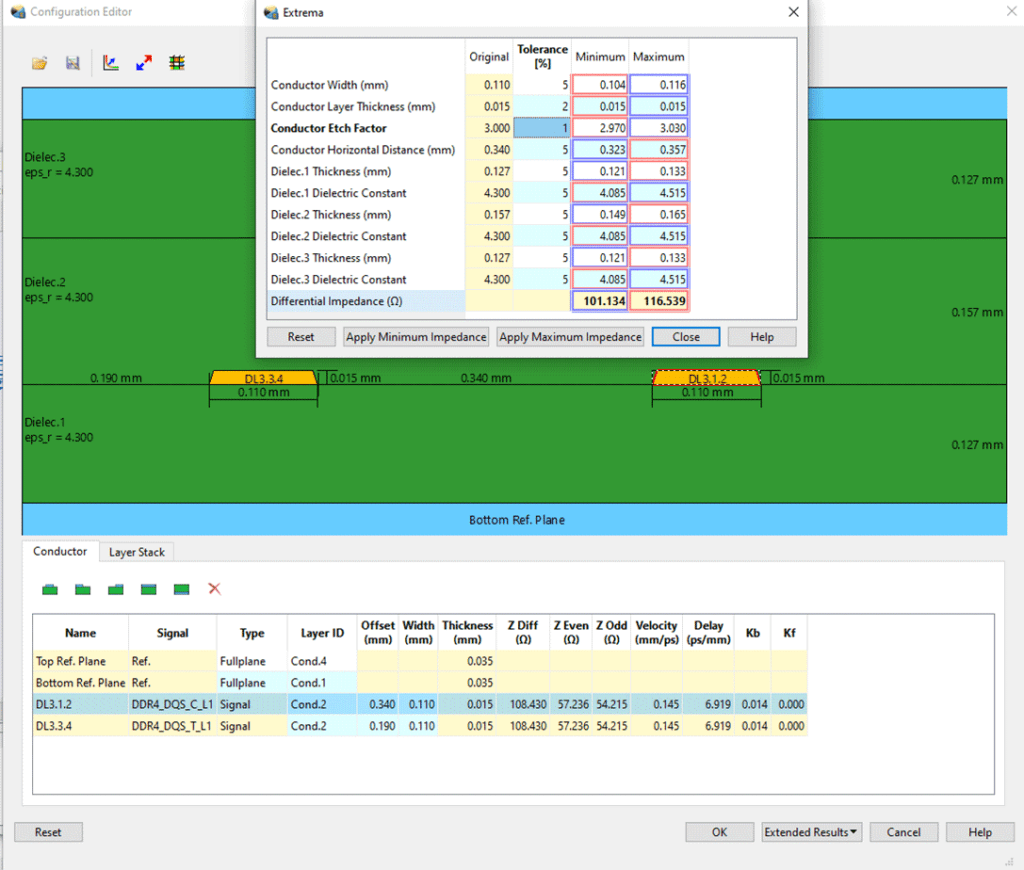

Our integrated EM field solver supports lossy interconnect models, manufacturing Tolerances, and material roughness, which empowers you to plan impedance meticulously. This approach minimizes signal loss and maximizes performance, ensuring your designs meet high standards.

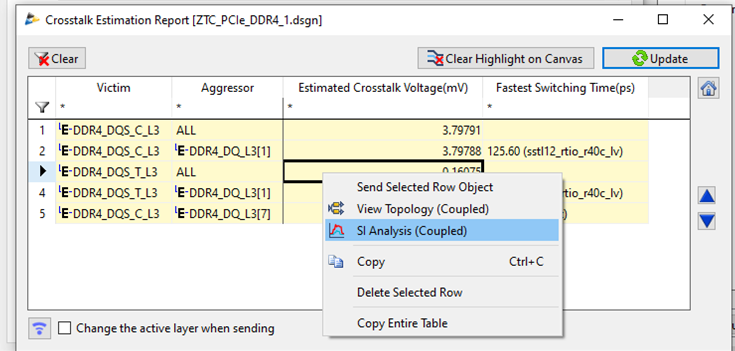

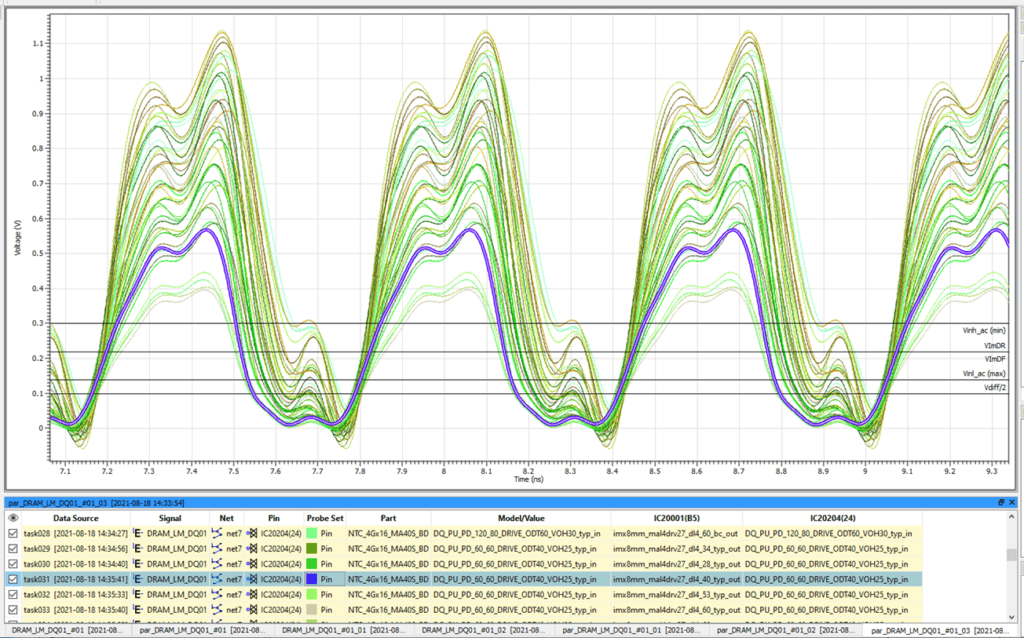

Experience rapid, interactive time-domain simulation that provides precise timing, reflection, and crosstalk analysis. Swiftly identify and rectify potential signal integrity issues, saving time and resources.

Efficiently manage your simulation library with a wide range of supported models, ensuring access to the necessary resources for accurate and reliable signal integrity analysis.

CR-8000 allows a fast crosstalk screening based on field solver results and assigned device models ( Crosstalk Estimation report), while a further detailed crosstalk simulation can be performed to proactively mitigate interference issues and preserve signal integrity.

Utilize SPICE and S-parameter-based models in the time domain, offering versatile modeling options for your signal integrity analysis, allowing you to tailor your approach to the specific needs of your project.

By utilizing IBIS buffer models, your analysis becomes highly compatible with industry standards, ensuring seamless integration into your workflow and adherence to established norms. The support of Power-Aware IBIS models allows to include effects like SSN (Simultaneous Switching Noise) in your analysis.

Fine-tune your design with parameter sweeps, allowing you to optimize your topology to meet specific requirements and ensure peak performance in various scenarios.

The usage of S-Parameter data in time domain simulation requires the transfer from time domain into frequency domain. This vector-fitting process is supported by AI/ML technology to identify best fitting parameters for the structure of interest.

Delve into the automatic timing, skew, and signal integrity measurement results to gain in-depth insights into your design’s performance.

Gain a comprehensive understanding of how manufacturing tolerances and material properties impact signal integrity behavior. This knowledge empowers you to make qualified design decisions for greater reliability.

Visualize signal quality with time-domain eye pattern analysis, offering a detailed picture of your design’s performance for both parallel busses and serial links.

Precisely inspect setup and hold timing to ensure that your data transmission is reliable and meets stringent timing requirements.

Set up eye masks to define signal quality standards and measure your signals against them. This process serves as a rigorous quality assurance step, ensuring your design meets predefined criteria.

Utilize Time Domain Reflectometry (TDR) analysis to optimize your interconnects, ensuring the reliability of signal transmission and reducing the risk of signal loss.

Thoroughly examine TDR impedances for both single-line and differential pair interconnects, identifying and addressing impedance mismatches to ensure signal integrity without the necessity of assigning IBIS buffer models to the devices (model-less signal integrity simulation).

Calculate wideband S-parameters for interconnect optimization, supporting frequencies up to 15 GHz. This capability ensures high-frequency performance and reliability.

Analyze mixed-mode S-parameters to gain a comprehensive understanding of signal behavior in complex scenarios, enhancing your ability to address potential issues.

Enforce causality in your S-parameter analysis where required, ensuring the accuracy and reliability of your simulation results.

Export S-parameters to Touchstone files for seamless integration with other simulation tools, streamlining your workflow and collaboration efforts.

Optimize gigabit SERDES channels with AMI simulation, ensuring the reliability of high-speed data transmission and reducing the risk of errors.

Calculate the Bit Error Ratio (BER) to ensure error-free communication in your high-speed channels, providing the ultimate assurance of performance reliability.

Characterize serial links comprehensively, including S-parameter analysis, transfer function analysis, and impulse response analysis, providing a holistic view of your channel’s performance.

Account for various types of jitter (deterministic jitter, random jitter) in both the transmit (TX) and receive (RX) paths, ensuring your design can tolerate jitter and maintain signal integrity.

Visualize eye patterns and bathtub curves to assess signal quality and reliability with clarity and precision.

Simplify the parameterization of AMI models, streamlining your simulation setup and enhancing user-friendliness.

Measure eye openings and signal-to-noise ratio (SNR) to quantify signal quality and assess the margin for error, ensuring your design meets performance standards.

Related Resources

In our webinar we will provide an introduction to the challenges of signal integrity and the underlying physical effects. This will provide the basis for practical tips to address the related challenges during PCB design.

ONTEC faced a difficult challenge: develop a multimedia broadcasting product while complying with a customer’s electromagnetic interference requirements, all within a tight development schedule. ONTEC used Zuken’s CR-8000 with Keysight’s ADS (including SiPro) to meet the requirements of the challenge

DDR5 is the latest generation of memory. In this joint webinar with Keysight Technologies, we’ll begin with pre-layout simulation, then transition to CR-8000. The design will then be verified by Electromagnetic (EM) simulation and system simulations in Keysight ADS, in order to build confidence in the final DDR5 design.