Graphical Pin Manager – FPGA/PCB Co-Design

Engineers continue to embrace programmable logical devices within their product designs in numerous applications across a wide range of industries. With FPGAs incorporating embedded processors, memory blocks and DSP functions, they are an attractive, low-cost option for many designs. FPGAs can now replace ASICs in many design applications. They are also used for prototyping designs, implementing ASICs, or other embedded hardware and software design as they can easily be reprogrammed. However, rising device complexity means high pin counts, which bring about new challenges and higher costs when integrating these devices into the PCB. Engineering teams require an effective design flow, unifying FPGA and PCB design to reduce design cycle times and improve time-to-market.

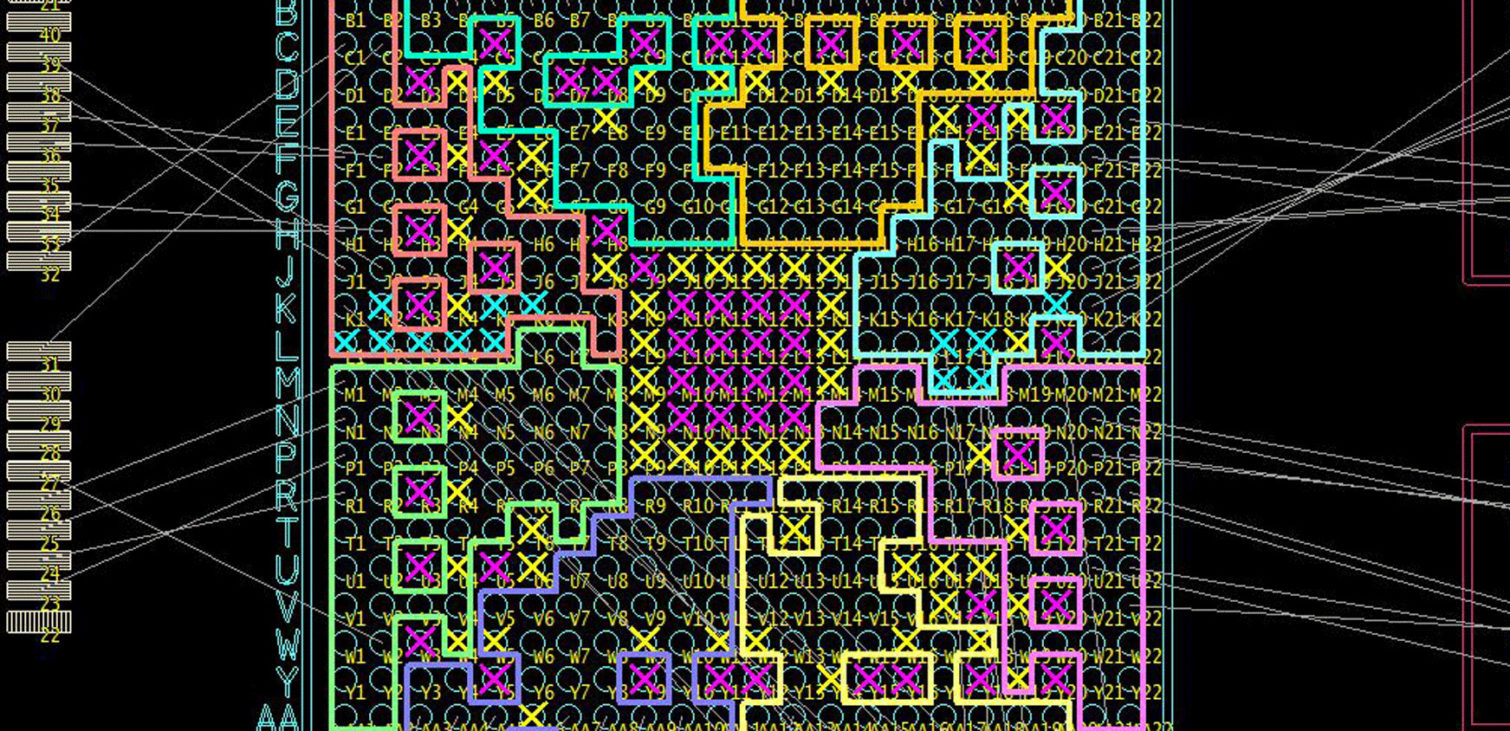

Zuken’s Graphical Pin Manager (GPM) offers an effective FPGA/PCB co-design environment, providing support for the latest devices offered by FPGA vendors such as Xilinx, Altera, Lattice, and Microsemi. As part of Zuken’s CR-8000 system level design suite, GPM enables design teams to intelligently communicate pin I/O assignment information on FPGAs or other high pin count devices with Design Gateway, Design Force and other FPGA vendor tools. This allows programmable devices to be developed in parallel with the PCB design and means these devices are ready to meet project delivery schedules and are available for production. GPM is also compatible with CR-5000 System Designer and Board Designer.

Top benefits and features

- Concurrent design flow for FPGAs and PCBs, from library creation to physical design

- Up-to-date support for Xilinx, Altera, Lattice and Microsemi device kits, including I/O constraints for accurate part development

- Accurate control and traceability of critical details for programmable devices using Project Management system

- Reduce part creation time with automatic creation and splitting of logic symbols and direct integration with Component Manager

- Reduce design iterations with direct exchange of pin constraint and report files from Altera Quartus II, Xilinx ISE/Vivado, Microsemi Libero, Lattice ispLever/Diamond and Aldec Active-HDL

- Automatic creation, editing and checking to reduce effort in design output

- Support for BSDL, CSV, VHDL/Verilog, and existing library data for high-pin count device design

- Optimize I/Os with interactive and automatic pin swapping

- Generate pin swap reports to compare document changes during FPGA and PCB design

Also see: