CADSTAR – Power Integrity Advance

Complexity of today’s design includes the growing counts of voltages, increasing switching currents from components, and more power consumption.

This makes the study of power integrity a vital part of the design flow. Analyzing the performance and EMC behavior of your electronic design requires not only taking into account the design of the circuitry and geometry of the layout, but also includes the quality of the power distribution system. Parasitic noise voltages on the power/ground system is caused by integrated circuit (IC) gate switching inducing a switching current that can lead to malfunctions and significant increases in electromagnetic emissions.

High-speed designs utilize numerous high pin-count ICs, like FPGAs and CPUs operating on multiple voltage rails and strict signal noise margins. Take into account the complex split planes to support these IC’s, identifying voltage drops within a power supply due to losses in copper has become a necessity. As these IC’s become more of a commodity in electronics applications, the fight for the board space required to successfully transmit signals gets more aggressive. Careful design of the power distribution system is now a critical state in the design flow.

CADSTAR Power Integrity Advance provides fast and practical power integrity and electromagnetic interference analysis within the real-time PCB design flow. With EMI, AC and DC power analysis combined in a single environment, you can determine the best decoupling and power distribution strategy for your pre-layout and post-layout stages with support for a complete what-if environment.

Top features and benefits

- Ensure quality and integrity of the power distribution system during and after layout

- Provide full board EMC screening for differential and common mode boardlevel EMC effects prior to production of the first prototype

- Accurate modeling of copper shapes for power delivery and noise transmission

- Simulate power distribution impedance profile over frequency and crosstalk hotspots for common mode noise

- Save cost and board space by reducing the number of decoupling capacitors

- Improve decoupling by determining correct distribution of capacitor values

- Indicate quality of placement location, value and trace/via connection

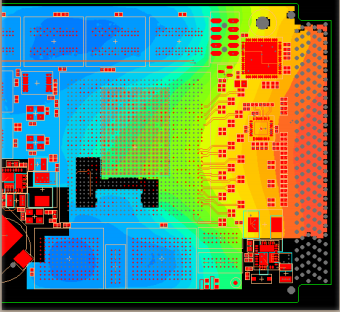

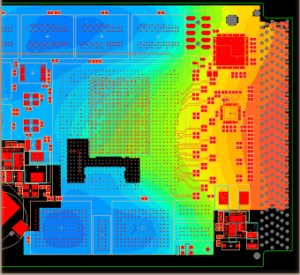

- Provide a clear graphical display of voltage and current distribution map for voltage drops and excessive current density