On-demand webinar

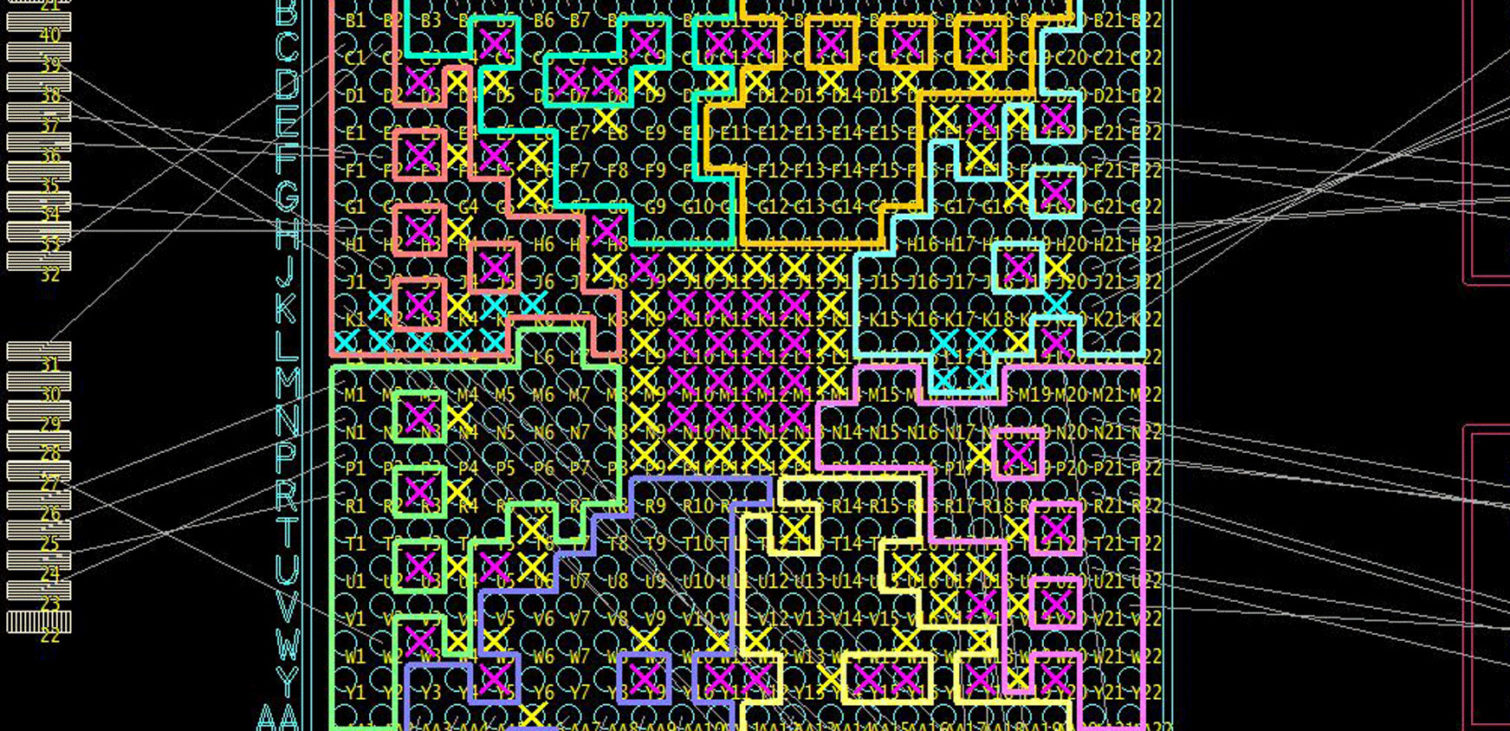

L’assegnazione dei pin dell’FPGA senza considerare il posizionamento e il routing dei componenti può non solo avere un impatto sui tempi, ma anche rendere il PCB inarrestabile. Questo webinar dimostrerà un efficace ambiente di co-design di FPGA/PCB utilizzando i più recenti dispositivi offerti dai fornitori di FPGA, come Xilinx, Altera, Lattice e Microsemi. I team di progettazione saranno in grado di comunicare facilmente gli I/O e di limitare le informazioni sugli FPGA o altri dispositivi ad alto numero di pin in qualsiasi momento durante il processo di progettazione.

Il webinar esplorerà vari punti del processo di progettazione in cui può avvenire il co-design dell’FPGA o di altri dispositivi programmabili e il layout della scheda; questo include la creazione di parti di libreria, l’immissione schematica, l’ottimizzazione degli I/O e la gestione dell’assegnazione dei pin durante il layout della scheda. Migliora il processo di progettazione e lo sviluppo di dispositivi programmabili in parallelo alla progettazione del PCB, eliminando inutili iterazioni di progettazione.

Cosa imparerai:

- Come ottimizzare l’assegnazione dei pin dell’FPGA per la progettazione di PCB

- Come condividere i dati di progettazione FPGA con gli ingegneri di layout in un approccio automatizzato e privo di errori

- Come condividere la connettività e l’assegnazione dei pin richiesti dal layout della PCB con i progettisti di FPGA

- Come la sincronizzazione dei dati tra FPGA, PCB e dati di progettazione schematica può evitare lo scambio manuale di informazioni.

A chi è rivolto:

- Engineering managers, hardware engineers, FPGA engineers, PCB designers

Durata:

- 36 minuti