## The TWO THINGS That Make Serial Links Work

...from 7 to 70 Gbps

Yes, just two things

Donald Telian telian@siguys.com

## The TWO THINGS That Make Serial Links Work

Why DO serial links work? In this talk, Donald Telian explains that the two things that make links work are also the things that make them fail. When not done right. High-speed links work electrically when you (1) deliver 10 mV accuracy from Tx to Rx, and (2) properly equalize at the system level. As such, this talk details the primary technical requirements necessary to get these right. With tens of thousands of links in production, Telian has found serial technology to be quite robust. Indeed, when these basic things are done, the links have always worked right the first time. Nevertheless, when engineers do not do these two things, he gets the call. Uniquely positioning him to explain why serial links work, why they fail, and – most importantly – what you need to do in the design phase to make them work.

Donald Telian has worked in Signal Integrity for more than 40 years. For the last 20 years he has been a Consultant, focused on designing serial links into products from flash drives to switches with thousands of links. He has invented various SI concepts, tools, and quirks engineers use everyday to get their jobs done. He is an SI Coach, the owner of SiGuys.com, and the author of "Signal Integrity, In Practice" – a new book and in-person 2-day class that cuts through the noise to explain how to "do" SI when confronted with the data rates of today.

## **Before We Begin**

Page number -

Section number ->

Time is limited today

- More info available in my book as shown here

- Even more info available at my LIVE workshops offered here:

## Agenda:

- 1. Why Serial Links Work

- 2. Why Serial Links Fail

- 3. How to Make Links Work

- 4. Welcome to Gen2 SI

## Agenda:

- 1. Why Serial Links Work

- Two Reasons

- 2. Why Serial Links Fail

- 3. How to Make Links Work

- 4. Welcome to Gen2 SI

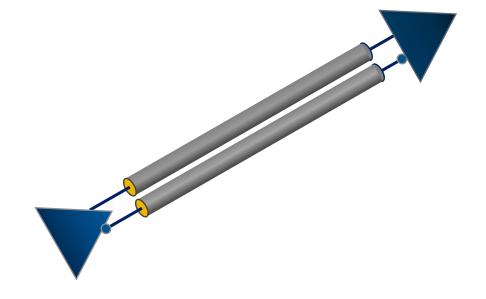

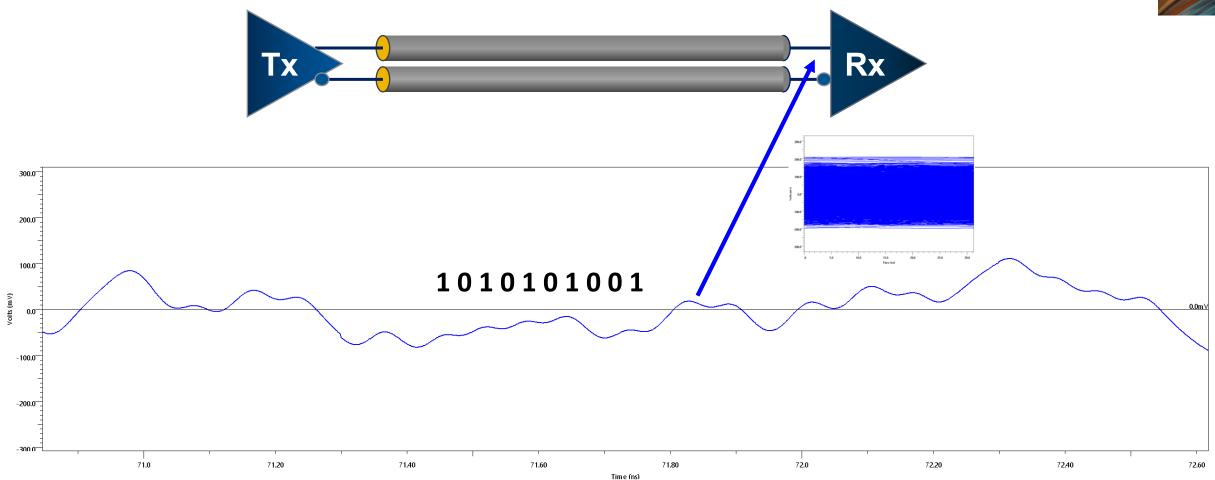

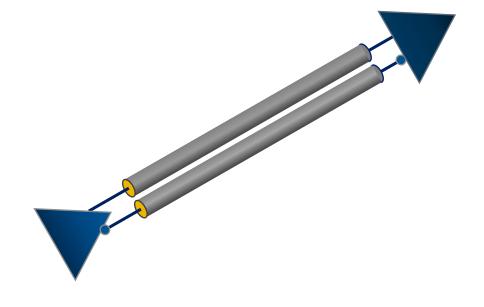

## A High-Speed Serial Link

Transmitter (Tx), Differential Connection (Channel), Receiver (Rx)

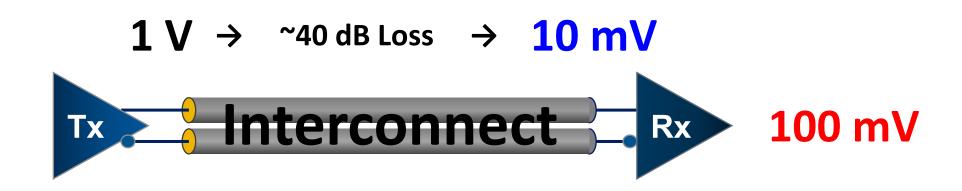

## Why Serial Links Work, #1

Because we transmit across PCBs (passives) with 10mV accuracy

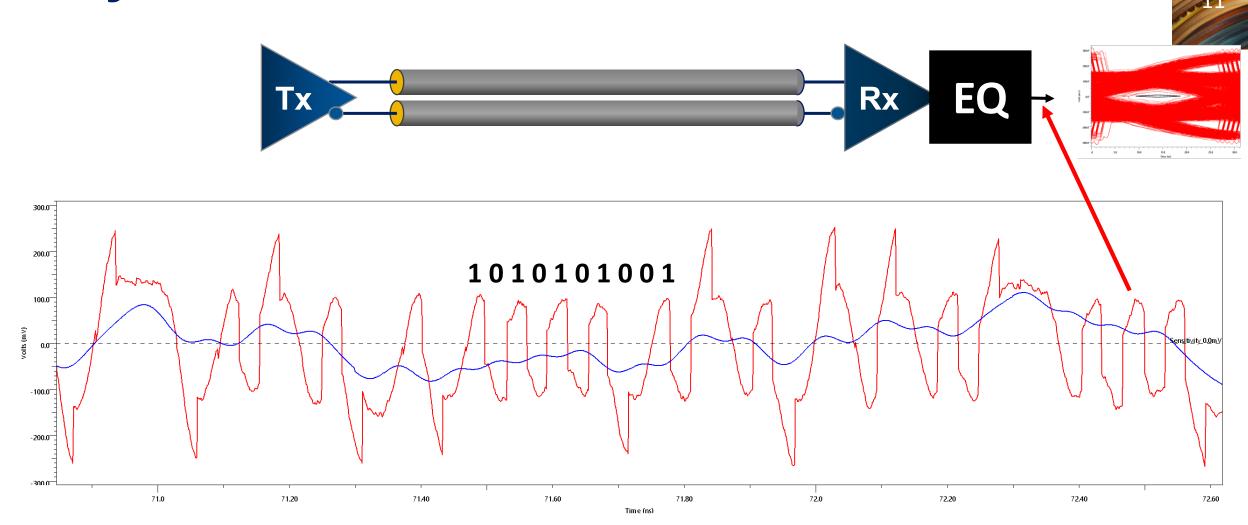

## Why Serial Links Work, #2

Because equalization (EQ) transforms our 10mV signals into logic levels

## Agenda:

1. Why Serial Links Work

2. Why Serial Links Fail

3. How to Make Links Work

4. Welcome to Gen2 SI

## Why Serial Links Fail?

Not surprisingly, the two reasons why serial links WORK are also the two reasons why they FAIL:

#1

INCORRECTLY CONFIGURED:

**EQUALIZATION (EQ)**

Must recover the digital signal

#2

INCORRECTLY MANAGED:

PASSIVE INTERCONNECT

Must preserve the analog signal

## Top THREE Reasons Why Serial Links Fail

1. Incorrectly Configured EQ

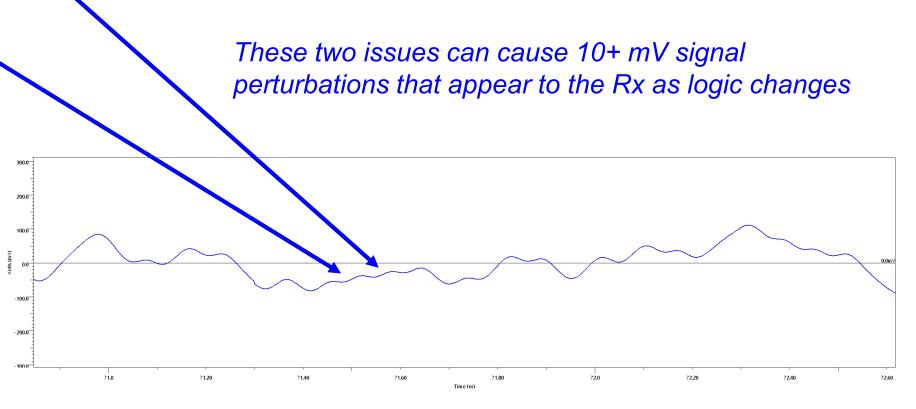

2. Discontinuities

3. Crosstalk

## Agenda:

- 1. Why Serial Links Work

- 2. Why Serial Links Fail

- - 3. How to Make Links Work

- 1. Configure EQ Correctly

- 2. Minimize Discontinuities

- 3. Control Crosstalk

- 4. Welcome to Gen2 SI

## **#1: Configure EQ Correctly**

- The Dream: ICs will optimize by themselves

- This challenge is very complex

- In practice, this doesn't work well. So what can be done?

- Step 1: Get access to Tx EQ software registers

- You can do this!

- Step 2: Turn off Tx EQ

- Sounds ridiculous? Oddly, this <u>has solved many</u> post-hardware serial link problems

#### **More EQ Detail**

- Educate yourself on the EQ "Alphabet Soup" (acronyms)

- CTLE, FFE, DFE, AGC, VGA, Taps/Cursors, CDR, etc.

- These terms are as important as: stackup, return current, flight time...

- Rx EQ has become extremely powerful

- Can handle much of the signal recovery problem by itself

- And is typically self-optimizing (simpler, less of a system-level problem)

- Redundant with Tx EQ, yet without amplitude penalty

- And higher-loss systems must preserve amplitude!

- Use Tx for "pre-cursor" EQ

- Something most Rx EQ cannot do

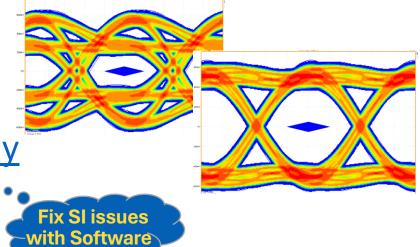

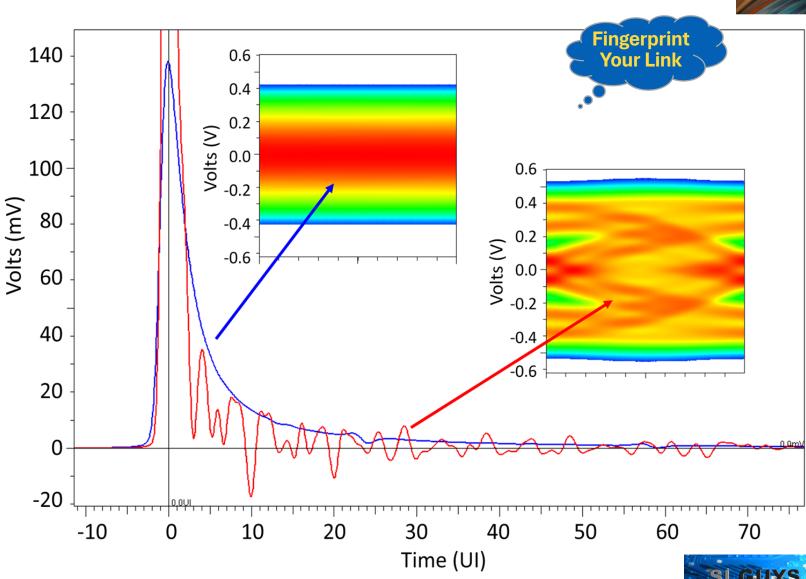

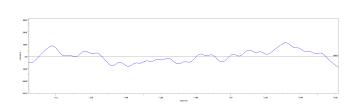

## **Channel Pulse Response = Fingerprint**

3.5.2 88

- Both Loss and Discontinuities close eyes

- As colors show for two different channels

- Pulse response reveals what type of channel you have

- And how to EQ/fix it!

- Great topic!

- Hands on @ my SI Class

- Today's EQ handles Loss better than Discontinuities

- So design them out!

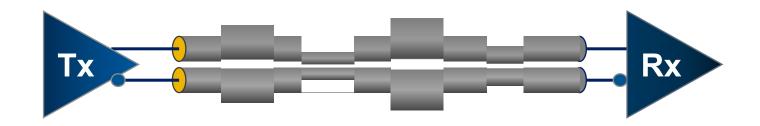

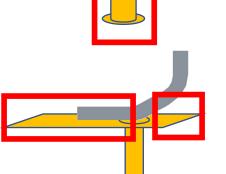

#### **#2: Minimize Discontinuities**

- In practice, a nice smooth connection from Tx to Rx doesn't exist

- Breakouts, AC capacitors, Connectors, Vias, etc. may present an impedance change

- Impedance changes cause signal "reflections" that damage SI

A "Discontinuity" occurs at any place in the connection where the impedance changes

### **Eight Ways To Fix a Discontinuity:**

- 1. Ignore it

- 2. Remove it

- 3. Match it

- 4. Equalize it

- 5. Shorten it

- 6. Distance it

- 7. Dampen it

- 8. Ground return it

Small Enough to Ignore?

Step 1: Minimize Discontinuities

<u>Understanding Via Impedance</u>

Fixing SI Issues in Software

Fixing Stubs

**Discontinuity Proximity Effect**

**Trading Loss & Discontinuities**

Proper Ground Return Vias

#### **RFS = Which Discontinuites Matter**

| Signal | Integrity   |

|--------|-------------|

|        | In Practice |

|        | 2.8         |

| F | 0 |

|---|---|

| כ | U |

|   | 1 |

| , |                                  |

|---|----------------------------------|

| 7 | Practical Handboo                |

| 6 | or Hardware, SI,<br>PGA & Layout |

|   | Ingineers                        |

|   | Donald Telian                    |

| 1   | Z  |

|-----|----|

| (   | 0  |

| _   | 5  |

|     | ~  |

| 1   | 1  |

| ~   | 2  |

| 7.7 | 11 |

| Feature                        | 4 (5) Gbps                                        | 8 Gbps   | 16 Gbps   | 32 Gbps    | 64 Gbps      | Unit  | SIiP Section  |

|--------------------------------|---------------------------------------------------|----------|-----------|------------|--------------|-------|---------------|

| Industry/PCIe terminology      | Gen2                                              | Gen3     | Gen4      | Gen5       | Gen6         |       | I.P.          |

| Fundamental Frequency          | 2                                                 | 4        | 8         | 16         | 16 (PAM4)    | GHz   | bo            |

| Relevant Feature Size          | 160                                               | 80       | 40        | 20         | 20           | mils  | 4.1, 2.1, 4.x |

| what's that?                   | traces                                            | vias     | conn pads | everything | everything   |       | 4.2, 4.3, 4.4 |

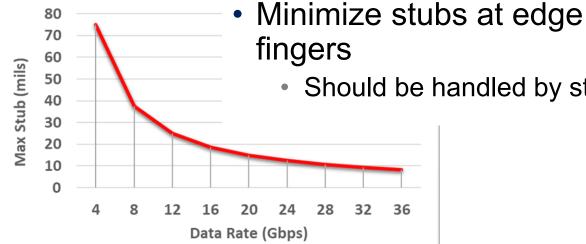

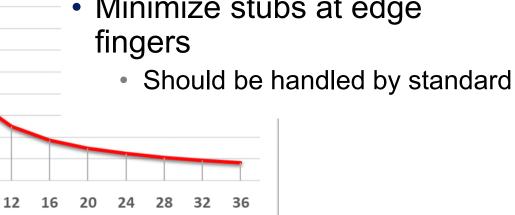

| Max Stub                       | 64                                                | 32       | 16        | 8          | 8            | mils  | 2.5, 1.3.3    |

| backdrills                     | none?                                             | seq-lam  | 2 layers  | per-layer  | per-layer    |       |               |

| P/N Matching, static           | 10                                                | 5        | 2         | 1          | 1            | mils  | 2.3           |

| Target Bit Error Ratio (BER)   | 1.E-12 1.E-06                                     |          |           |            |              |       |               |

| Route Style                    | 45°                                               | 45°      | curved    | curved     | curved       |       | 2.4           |

| Diff-pair Spacing (XY/Z, min)  | 25                                                | 25       | 25        | 30         | 30           | mils  | 5.3           |

| Insertion Loss (max)           | 16                                                | 22       | 28        | 36         | 32           | dB    | 2.2, 3.5      |

| Min EQ: Tx_FFE/Rx_states, CTLE | 1/0                                               | 2 / 1, C | 2 / 2, C  | 2/3,C      | 3 / 16, C+   | #taps | 3.3, 3.4, 2.7 |

| Lengt tch metho                | serpentines irregular spaced bumps                |          | ımps      |            | 2.4          |       |               |

| Fiberglass wear                | spread glass and rotate image 12 degrees on panel |          |           |            | 2.6          |       |               |

| GND Return Vias (GRVs)         | within 30 mils of signal layer transition         |          |           |            | [48a, 3.2.2] |       |               |

| Solid GND reference layers     | both sides of trace (don't use microstrips)       |          |           |            | 2.3, 2.6     |       |               |

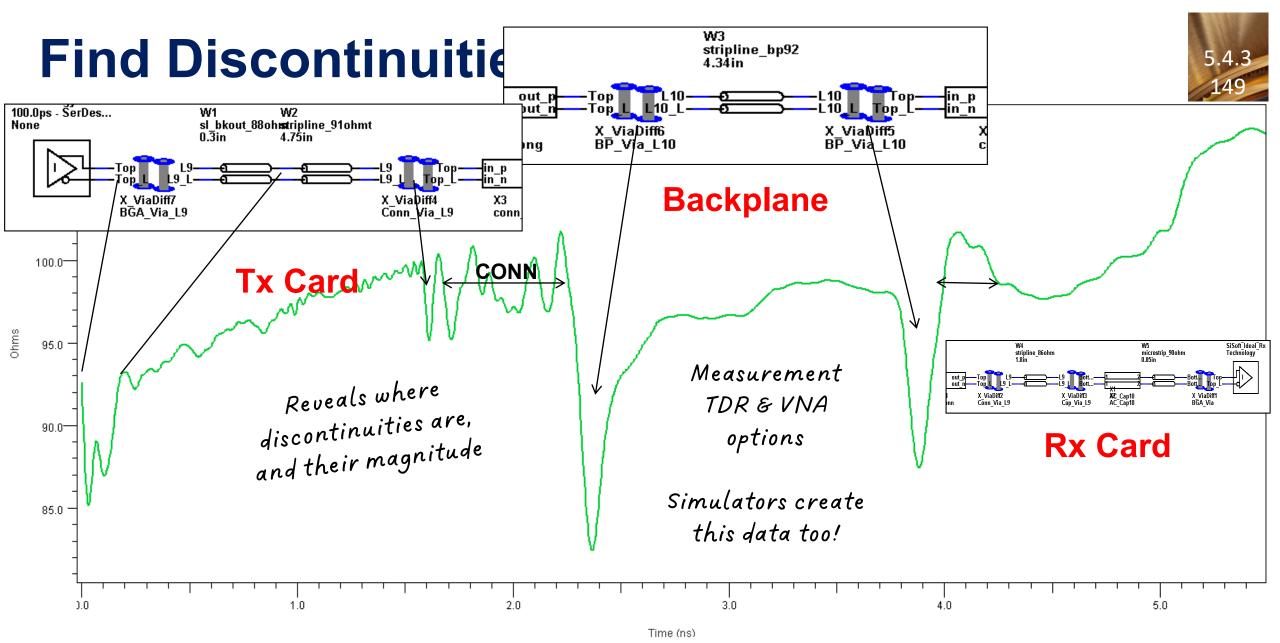

TDR is a great way to isolate & quantify discontinuities

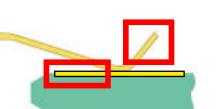

#### **Stubs: Bad Discontinuities**

8 to 16 Gbps failures

Remove stubs at solder pads

25 to 64 Gbps failures

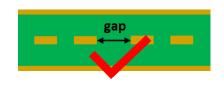

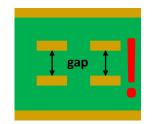

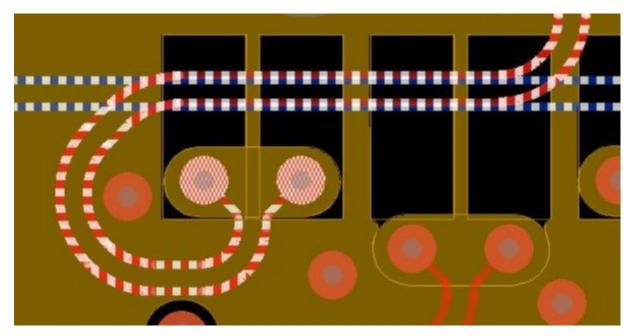

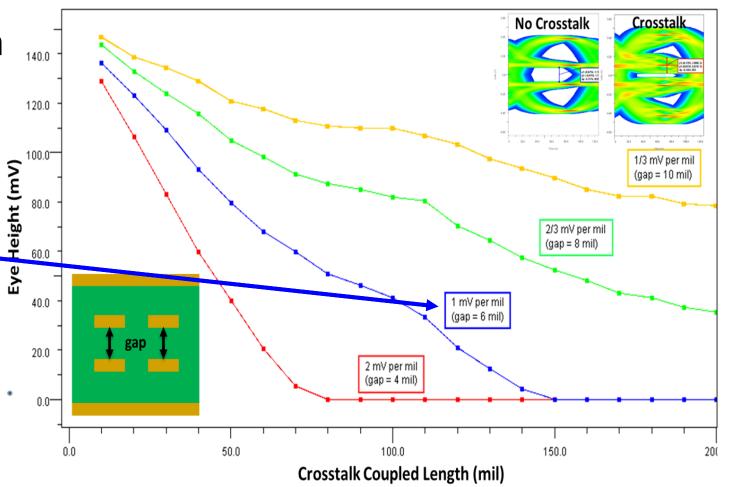

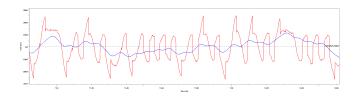

#### **#3: Control Crosstalk**

- Not where you expect

- Plane cutouts

- Used to match impedance

- Connector and Cap pads

- Cap Void Example

- Near-end Tx (red)

- Far-end Rx (blue)

- Combined coupling = 120 mils

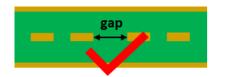

Always use route keepouts under voids, shields, 30+ mil gaps

Best fix I've found is to visually check layer to layer

#### 10 mV Accumulates Fast!

Eye height vs coupled length

Colors are gap distances

- 6 mil gap:

- Typical PCB distance

- 1 mV per 1 mil of coupling

- Can close an eye

## Agenda:

- 1. Why Serial Links Work

- 2. Why Serial Links Fail

- 3. How to Make Links Work

- 4. Welcome to Gen2 SI

## Serial Links Define "High-Speed"

- Serial Links have changed the way we "do" signal integrity (SI)

- I've simplified this new practice into "Gen2 SI"

- Serial revolution began in ~2001

- Began at 1 Gigabits per second (Gbps), now 50+ Gbps

- 2002 Intel declares: cheaper to use transistors than PCB traces

- Silicon integration becomes continual enabler of higher bandwidth

Silicon Integration Enabled Gen2 SI

# Signal Integrity

## Silicon Integration

Signal Integrity + Silicon Integration = SI + SI = Gen2 SI

## Technical Comparison

- ICs  $\rightarrow$  1,000,000x

- PCBs  $\rightarrow$  4x

- Data Rates  $\rightarrow$  5,000x

In practice,

SI is simpler now

with Gen2 SI

| Gen1 Signal Integrity    | Gen2 Signal Integrity   |  |  |

|--------------------------|-------------------------|--|--|

| 1986 to 2006             | 2007 to Present         |  |  |

| Parallel                 | Serial                  |  |  |

| 8 MHz to 3 GHz           | 4 to 70 GHz             |  |  |

| System of ICs            | IC dictates System      |  |  |

| Mysterious "black magic" | Basic Science           |  |  |

| Buffer VI/Slew           | SerDes Equalization     |  |  |

| Trace Length Rules       | P/N Symmetry            |  |  |

| Common & Source Clocks   | Recovered Clock         |  |  |

| AC Timings               | Eye Diagrams, BER       |  |  |

| Topology / Termination   | Point-to-Point          |  |  |

| Trace Impedance          | Feature Impedance       |  |  |

| Flight Time              | Loss, Discontinuities   |  |  |

| Ground Planes            | Ground Returns/Grids    |  |  |

| Stackup                  | Weave & Copper Profiles |  |  |

## **LIVE SI Class Teaching Tour!**

- Munich Germany Oct 29 & 30 2025

- In partnership with Zuken

- Private/Corporate Classes Too!

"out of the design cave"

## **How I Can Help:**

https://siguys.com/

Available at Amazon

Hardcover or Kindle

## THANK YOU

Let's achieve Signal Integrity, in Practice

Donald Telian

telian@siguys.com

Copyright © 2025, SiGuys, Slide 29