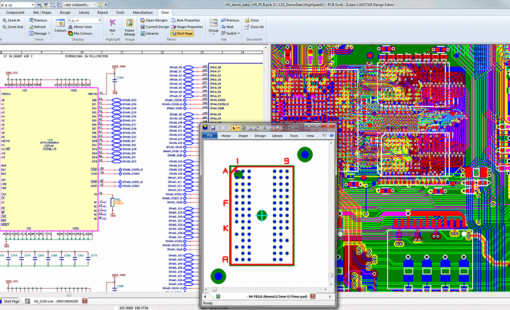

Schematic capture with placement and constraint planner

CADSTAR is a complete software environment for PCB design – from initial concept through to product realization. With a unified suite of applications, engineers can seamlessly define, visualize, implement and verify their designs.

Schematic capture with placement and constraint planner

Constraint-driven interactive and automatic PCB layout routing

Signal Integrity, Power Integrity, and Electromagnetic Compatibility (EMC)

Comprehensive markup and post-processing capabilities

With CADSTAR's unified suite of applications, engineers can seamlessly define, visualize, implement and verify their designs.

CADSTAR Schematics is a highly integrated front-end solution, providing a smooth and error-free transition (forward & back annotation) between schematics and PCB, easy to learn and use for both occasional and frequent users.

Easy to learn and fast to use, the constraint driven approach of CADSTAR PCB design layout software helps you create right-first-time printed circuit board designs.

With its Board Modeler Lite, CADSTAR bridges the gap between electronic and mechanical design allowing PCB designers to work in a 3D environment, perform collision checks between components, boards and enclosure and make placement changes to resolve them.

With a mix of manual, auto-interactive and automatic tools for PCB placement and routing, the CADSTAR Place and Route Editor 2000 has been optimized for performance, quality and manufacturability to meet today’s advanced technology design challenges.

With its highest performing routing tool, Route Editor XR 5000HS, CADSTAR offers specific additional functionality targeted for high-speed PCB design, such as DDR2, DDR3, DDR4 and PCI Express, including min/max length, skew, delay and crosstalk limits to meet tight timing and noise margins.

Zuken’s CADSTAR solution integrates a design migration tool within all bundles, which includes additional features to better support and exploit legacy design data. Designs can be imported from a number of third-party packages, including:

Zuken’s free PCB Design Software, CADSTAR Express, provides a quick and easy way for you to experience the basic features of our standard single-board PCB design software solution, CADSTAR.

CADSTAR Design Viewer is a free download that lets you share and access CADSTAR design data very easily on any of your preferred Windows platforms.

CADSTAR Professional is Zuken’s integrated schematic and PCB design solution for HDI and high-speed layout, with advanced layout capabilities that enable the design engineer to quickly and effectively realise design intent.

CADSTAR Basic is Zuken’s integrated schematic and PCB design solution that provides layout specialists with a comprehensive toolset for integrated 3D MCAD/ ECAD design.

CADSTAR Lite is Zuken’s affordable integrated schematic and PCB design solution.

A selection of CADSTAR Datasheets

CADSTAR Schematic Capture provides a fast, efficient way to capture design intent, rules and constraints for smooth and error-free transition to PCB layout for product realization.

Easy to learn and fast to use, CADSTAR delivers high performance PCB layout to your desktop.

The matrix describes the features associated with each CADSTAR Place and Route Editor bundle.

As more designs incorporate high-speed technologies and involve integrated circuits (ICs) with rapidly increasing fast edge rates, the need for signal integrity analysis has become a vital part of the product development cycle.

Complexity of today’s design includes the growing counts of voltages, increasing switching currents from components, and more power consumption. This makes the study of power integrity a vital part of the design flow.

As PCB designs become more sophisticated and the design cycles ever smaller, it is imperative that the PCB design can satisfy the global market place and the numerous product options.