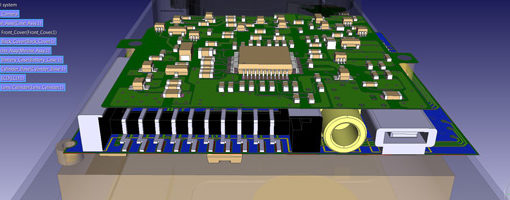

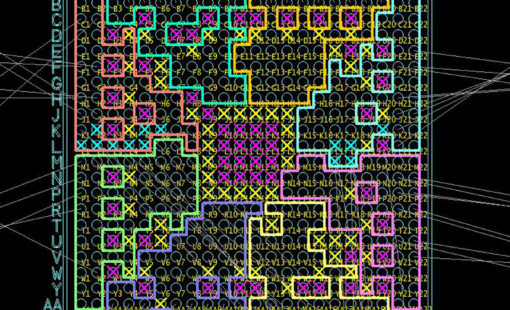

Multi-Board Constraint Browser zum Anzeigen und Analysieren von Verbindungen auf Systemebene

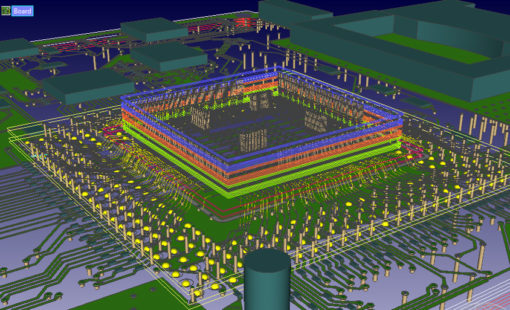

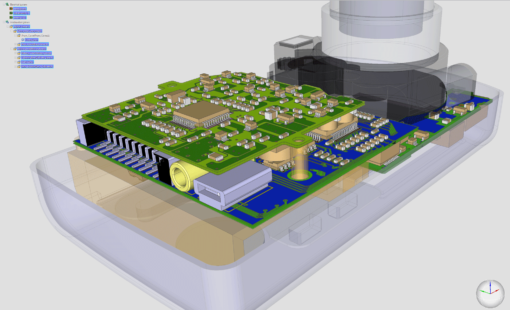

Zusätzlich zu den hochentwickelten Funktionen für das PCB-Layout bietet Design Force die Möglichkeit des Co-Designs von Chips, Gehäusen und Leiterplatten, so dass ein hierarchisches 3D-Design in Echtzeit ermöglicht wird. Auf diese Weise können Entwicklungsteams parallel jede beliebige Kombination aus fortschrittlichen Stack-Düsen, Gehäusen und elektrischen Leiterplatten erstellen.

Multi-Board Constraint Browser zum Anzeigen und Analysieren von Verbindungen auf Systemebene

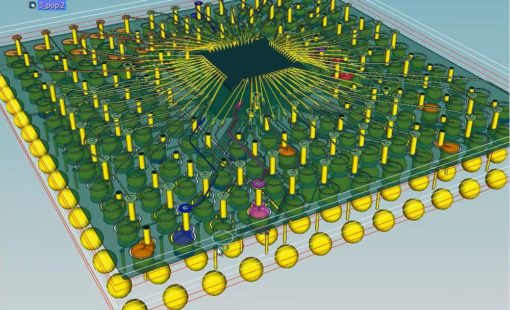

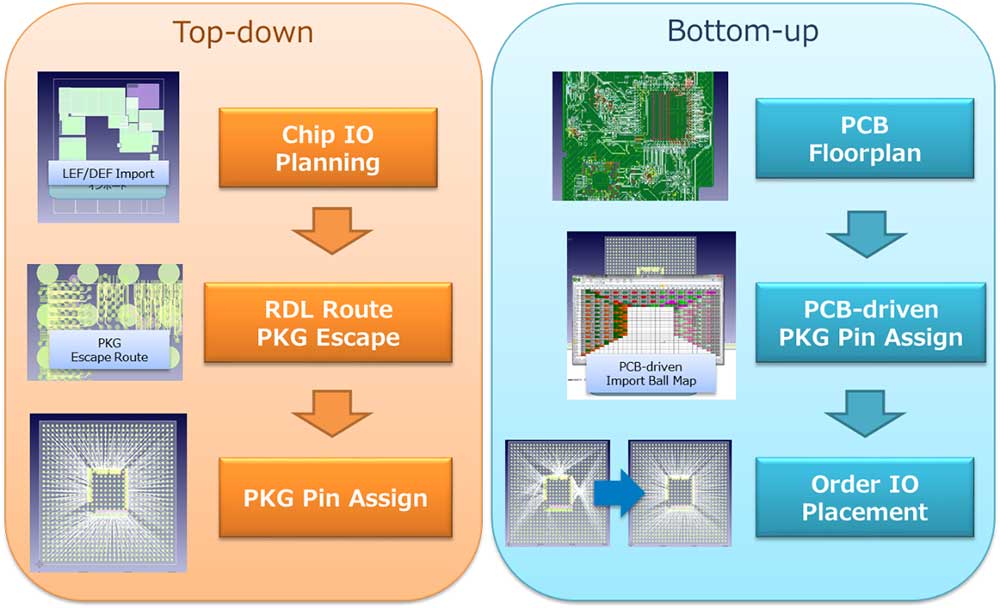

Automatische Zuordnung von Ball-Grid Kontakten mit der Fähigkeit, komplexe Routingmuster zu optimieren

Eine durchgängige Entwicklungsumgebung für Hochgeschwindigkeitsdesigns mit Constraint-Management und SI- und PI-Analyse

Leistungsstarke Routing-Werkzeuge für schnelle Machbarkeitsstudien und detaillierte RDL- und Bump-Muster für Signalpfade und Strom- und Masse-Netze

Ein ganzheitliches System-Co-Design berücksichtigt die Interaktion zwischen Chip-, Gehäuse- und Board-Daten, um Komplexität, Größe und Kosten des Gesamtsystems zu reduzieren.

Design Force Chip-, Package- und Board-Co-Design bietet eine technologiegerechte Designumgebung für die Implementierung von herkömmlichen wie innovativen Designstrukturen von elektrischen Leiterplatten, wie Die + Package + PCB, SiP, PiP sowie Interposer + TSV.

Design Force Chip-Package-Board Co-Design bietet eine einheitliche Umgebungslösung für maximale Systemoptimierung.

Design Force unterstützt die Integration in führende Analysetools von Partnern wie ANSYS, AWR, Agilent und Synopsys für RF, Full Wave FD/TD, Power Integrity sowie thermische Extraktion und Analyse. Dies ermöglicht es Designern, wichtige Probleme frühzeitig im Designprozess zu lösen.

Post-Layout-Extraktion von einzelnen und gekoppelten (Crosstalk) gerouteten Leiterbahnen; What-if-Analyse; Querschnittsansichten von Leiterbahnen.

Eine Simulationsumgebung für die Analyse der Signalintegrität nach dem Layout.

Eine leistungsstarke PCB-FPGA Co-Design-Umgebung, die den Austausch von I/O- und Constraint-Informationen zwischen PCB-Designs und FPGA-Designs ermöglicht.

Eine Simulationsumgebung für Power Integrity (AC-Impedanz und Entkopplungseffekt, DC-Spannungsabfall, Stromanalyse) und elektromagnetische Störungen (EMV-Vollausschirmung, Differenzmodus, Gleichtakt, Strombusrauschen).

Schnelle und einfache Überprüfung der Stromdichte einer Layoutstruktur auf ein bestimmtes Maximum.

Zugehörige Resosourcen

Webinars, Blogs, Pressemitteilungen

Schwerpunkte bei der Entwicklung des CR-8000 2020 waren die Steigerung der Designeffizienz, die Bereitstellung umfassender Design- und Verifikationsmöglichkeiten auf Systemebene sowie die Unterstützung der jüngsten Fortschritte in der Hardware-Packaging-Technologie.

Zugehörige CR-8000 Produkte

Zusätzlich zum Multi-Board PCB Design unterstützt Design Force auch die Entwicklung von IC Packages für Wire-Bond, Flip-Chip und High-Density Advanced Packaging

Der Graphical Pin Manager von CR-8000 bietet eine effektive FPGA/PCB Co-Design-Umgebung für die neuesten Bauelemente von Anbietern wie Xilinx, Intel, Lattice und Microsemi.

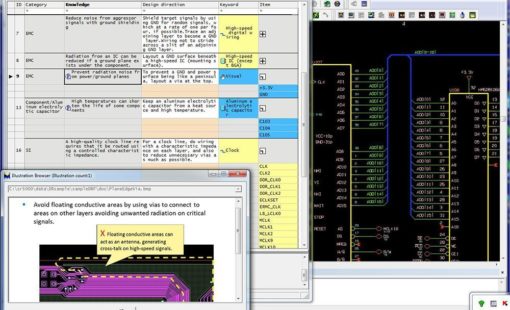

CR-8000 Circuit DR Navi hilft Design-Teams, technisches Fachwissen und PCB Design Best Practices in einer zentralen Datenbank zu bündeln, die in den Designprozess eingebunden ist.

Design Force kombiniert konventionelles 2D-Design mit nativem 3D-Design und den neuesten Technologien in Benutzeroberfläche und Grafik für schnellstes Rendern und Aktualisieren.